## ARL-4AC: Linha de Recombinação Aproximada por meio de Compressores Somadores 4-2 e 3-2 Aproximados

FELIPE HOFFMANN LARANGEIRA<sup>1</sup>; RODRIGO LOPES<sup>2</sup>;

MORGANA DA ROSA<sup>3</sup>; EDUARDO DA COSTA<sup>4</sup>; RAFAEL SOARES<sup>5</sup>

<sup>1</sup>Universidade Federal de Pelotas – [frlarangeira@inf.ufpel.edu.br](mailto:frlarangeira@inf.ufpel.edu.br);

<sup>2</sup>Universidade Federal de Pelotas – [rmdlopes@inf.ufpel.edu.br](mailto:rmdlopes@inf.ufpel.edu.br);

<sup>3</sup>Universidade Católica de Pelotas – [morganamacedoazevedorosa@gmail.com](mailto:morganamacedoazevedorosa@gmail.com);

<sup>4</sup>Universidade Católica de Pelotas – [ecosta.dacosta@gmail.com](mailto:ecosta.dacosta@gmail.com);

<sup>5</sup>Universidade Federal de Pelotas – [rafael.soares@inf.ufpel.edu.br](mailto:rafael.soares@inf.ufpel.edu.br);

### 1. INTRODUÇÃO

Diversos componentes aritméticos utilizam somadores compressores aproximados (AxACs) com o objetivo de aumentar a eficiência dos circuitos e maximizar a frequência de operação (da Rosa, 2022). Pesquisas extensivas têm explorado os AxACs, especialmente em aplicações tolerantes a falhas, como multiplicadores, sistemas de fornecimento de energia e unidades de gerenciamento de potência (Akbari, 2017), demonstrando melhorias significativas no produto potência-atraso (PDP), além de reduções no consumo de energia e na área ocupada. Adicionalmente, os AxACs também têm sido integrados em aplicações de processamento de imagem e vídeo, como os algoritmos de soma das diferenças absolutas (SAD) e soma das diferenças transformadas absolutas (SATD). Este trabalho propõe uma nova metodologia de aproximação para somadores de N bits com quatro entradas, denominada ARL-4AC. Diferentemente dos compressores somadores aproximados convencionais de quatro entradas, os quais geralmente aplicam aproximação apenas na primeira fase de computação mantendo uma linha de recombinação exata, o ARL-4AC proposto incorpora uma linha de recombinação aproximada utilizando compressores 3-2 exatos (3-2 ACs) e aproximados (3-2 AxACs). Essa abordagem inovadora, ainda não explorada na literatura, possibilita reduções no consumo de potência e na área do circuito, mantendo uma precisão aceitável. O ARL-4AC proposto, com linha de recombinação aproximada, supera arquiteturas existentes em termos de eficiência energética e de área em 5 dos 8 níveis de aproximação avaliados. Como estudo de caso, investiga-se a aplicação do ARL-4AC em uma Transformada Discreta do Cosseno (DCT) voltada ao processamento de imagens.

### 2. METODOLOGIA

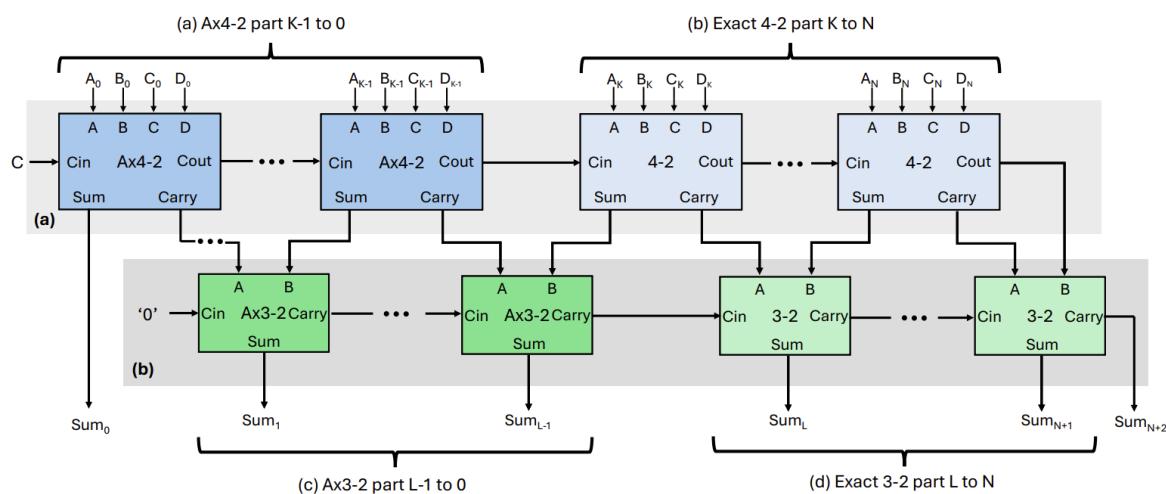

Esta seção apresenta nosso novo somador de N bits com quatro entradas, denominado ARL-4AC, ilustrado na Fig. 1, que emprega diferentes níveis de aproximação na primeira fase do somador (Fig. 1-(a)) e na linha de recombinação, denominada segunda fase (Fig. 1-(b)). De modo geral, trabalhos anteriores realizam aproximações apenas na primeira fase do ARL-4AC, enquanto a linha de recombinação é composta pelo método de adição fornecido pela ferramenta de síntese. Nossa proposta inovadora emprega compressores 3-2 exatos (ACs) e aproximados na linha de recombinação, conforme ilustrado na Fig. 1. A adoção dessa nova metodologia, substituindo o operador “+” da ferramenta de síntese por ACs e AxACs, possibilita uma melhora significativa em termos de economia de área e potência, uma vez que se torna viável aplicar aproximações em novos componentes do somador de N bits. Foram selecionadas as arquiteturas 4-2 e 3-2 mais relevantes analisadas neste trabalho, incorporados tanto na primeira fase

computacional do ARL-4AC (Fig. 1-(a)) quanto na segunda fase (Fig. 1-(b)), ambas seguindo a abordagem GFAC (Somadores sem portas lógicas).

O ARL-4AC proposto, com linha de recombinação aproximada, é definido por três variáveis ( $N$ ,  $K$ ,  $L$ ), onde  $N$  representa o número de bits nas entradas,  $K$  corresponde à quantidade de compressores 4-2 da primeira fase substituídos por 4-2 GFAC, iniciando pelos bits menos significativos, e  $L$  refere-se ao número de compressores da segunda fase substituídos por 3-2 GFAC. Para demonstrar a confiabilidade dessa nova metodologia, foram selecionados os somadores de melhor desempenho disponíveis na literatura, com o objetivo de alcançar o melhor compromisso entre eficiência e precisão. Assim, este estudo utiliza a arquitetura mais promissora proposta na literatura, sendo o 4-2 GFAC empregado na primeira fase e o 3-2 GFAC na segunda fase. Apesar de ambas as estratégias envolverem apenas fios, elas demonstram resultados excepcionais em termos de precisão em diversos níveis de aproximação, além de proporcionar economias expressivas no circuito.

Fig. 1. Exemplo de uma implementação em  $N$  bits da linha de recombinação aproximada na proposta do compressor somador aproximado 4-2 (ARL-4AC). (a) 1<sup>a</sup> fase do somador composta por 4-2 ACs e GFAC 4-2 e (b) 2<sup>a</sup> fase do somador composta por 3-2 AC e GFAC 3-2.

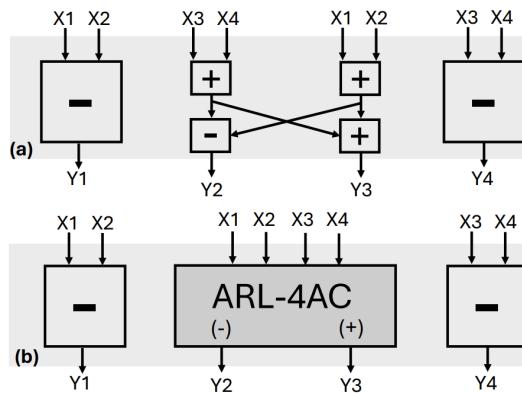

A Fig. 2 apresenta a DCT original em (a) e a arquitetura proposta com quatro entradas e quatro saídas em (b), sendo que dois componentes de subtração com duas entradas realizam as operações  $X_1 - X_2 = Y_1$  e  $X_3 - X_4 = Y_4$ . A inovação da proposta está nas saídas  $Y_2$  e  $Y_3$ , cuja computação é substituída pela arquitetura ARL-4AC, conforme ilustrado na Fig. 2(b). Como exemplo, na saída  $Y_2$ , o ARL-4AC realiza a equação  $(X_3 + X_4) - (X_1 + X_2) = Y_2$  apenas negando as entradas  $X_1$  e  $X_2$ , enquanto a entrada  $C$  (mostrada na Fig. 1) é configurada como '1', resultando na subtração esperada. Para a computação da saída  $Y_3$ , a entrada  $C$  é configurada como '0', realizando a operação de adição típica, ou seja,  $X_1 + X_2 + X_3 + X_4 = Y_3$ . Essa arquitetura permite a aplicação de métodos de aproximação nos componentes ARL-4AC, promovendo maior eficiência do circuito.

Fig. 2. Estrutura da DCT: (a) arranjo original, (b) nossa proposta ARL-4AC.

### 3. RESULTADOS E DISCUSSÃO

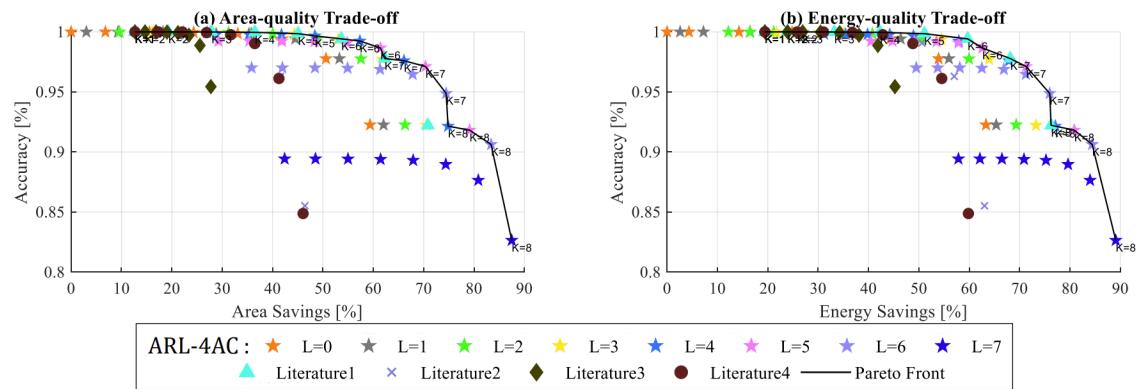

Foram analisadas 1.000.000 de amostras pseudorrandômicas de 8 bits para cada variável de entrada. Conforme mostrado na Fig. 3, a arquitetura proposta neste trabalho supera os AxACs da literatura em relação à área requerida nos níveis mais altos de aproximação, como nos casos em que  $K$  varia de 4 a 8. Como mencionado anteriormente, isso é aceitável, uma vez que o operador de adição fornecido pela ferramenta apresenta melhor eficiência do que o compressor somador 3-2. No entanto, o AxAC 3-2 utilizado no ARL-4AC apresenta elevada eficiência. Como os AxACs substituem os ACs, os ganhos na eficiência do circuito, juntamente com o impacto reduzido na precisão geral, tornam-se bastante significativos. Destaca-se, por exemplo, a arquitetura com os parâmetros  $K$  igual a 5 e  $L$  igual a 4, que atinge 99,7% de precisão e uma economia de área de 45,5% em comparação à arquitetura de referência. Da mesma forma, a configuração com  $K$  igual a 7 e  $L$  igual a 5 apresenta mais de 97,2% de precisão e uma impressionante economia de área de 70,2%, indicando o início de um padrão em que a primeira fase do somador deve ser maior que a segunda fase. A maior redução de área observada entre todos os somadores analisados ocorre para  $K$  igual a 8 e  $L$  igual a 7, superando 96%. Esses resultados comprovam a confiabilidade do somador proposto, oferecendo um melhor compromisso entre precisão e eficiência em relação às arquiteturas concorrentes. Por exemplo, para  $K$  igual a 7, a arquitetura DQ4-2C2 (Akbari, 2017), atinge 97,8% de precisão e uma economia de área de 62,3%, ou seja, 7% inferior à arquitetura com  $K$  igual a 7 e  $L$  igual a 5, com uma diferença de apenas 0,6% em precisão. Para  $K$  igual a 6 e  $L$  igual a 5, a primeira arquitetura supera os somadores da literatura, alcançando 98,6% de precisão e 62,6% de economia energética. Esse padrão também se repete para  $K$  igual a 7 e  $L$  igual a 5, e  $K$  igual a 6 e  $L$  igual a 6, com uma excelente precisão de 94,9% e economia energética de 76%. A arquitetura com os melhores resultados em economia de energia corresponde a  $K$  igual a 8 e  $L$  igual a 7, atingindo uma economia considerável de 97,4%. Esses resultados confirmam que a condição  $K$  maior que  $L$  garante boa precisão e uma arquitetura mais eficiente energeticamente na segunda fase do somador, em comparação ao uso convencional de compressores 3-2 na linha de recombinação. Este estudo projetou a DCT utilizando VHDL, com frequência de operação de 100 MHz e tensão de 1,25 V, empregando a biblioteca comercial de células padrão da ST com tecnologia de 65 nm. Foram utilizadas 100 imagens do conjunto de dados

CLASSICS. Os resultados consideram a DCT exata (apresentada na Fig. 2-(a)) como base de comparação, a DCT com a nossa arquitetura ARL-4AC (em cinza na Fig. 2-(b)) e as arquiteturas da literatura que utilizam técnicas AxC para garantir maior eficiência do circuito da DCT.

Fig. 3. Análise da fronteira de Pareto do ARL-4AC. (a) Compromisso entre área e acurácia e (b) Compromisso entre energia e acurácia, mostrando a acurácia em relação à área e à economia de energia para diferentes níveis de aproximação ( $L = 0$  a  $L = 7$ ).

#### 4. CONCLUSÕES

Este estudo propôs uma abordagem inovadora em somadores aproximados, com a introdução de uma linha de recombinação aproximada, trazendo avanços para as arquiteturas de adição de  $N$  bits. A proposta apresentou resultados notáveis em comparação com componentes altamente competitivos utilizados na parte exata da linha de recombinação. A arquitetura ARL-4AC demonstrou sua confiabilidade na aplicação à DCT, obtendo resultados superiores em relação às arquiteturas de última geração, alcançando mais de 67% de economia de potência e área, além de apresentar uma excelente resiliência a erros, com erro máximo de  $2,6 \times 10^{-143}$ .

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

Da Rosa, M. AxPPA: Approximate parallel prefix adders, **IEEE Transactions on Very Large Scale Integration (VLSI) Systems**, vol. 31, n. 1, pp. 17–28, 2022.

Akbari, O. . Dual-quality 4:2 compressors for utilizing in dynamic accuracy configurable multipliers, **IEEE Transactions on Very Large Scale Integration (VLSI) Systems**, vol 25, no. 4, pp. 1352–1361, 2017.

G. Levkine (2011), “*Mathship technologies corporation - test images collections: Collection of classic and old classics test images.*”. Disponível em: <https://www.hlevkin.com/hlevkin/06testimages.htm>