# ACELERADOR COM REAPROVEITAMENTO DE HARDWARE MULTIVERSÃO DE BAIXO CONSUMO PARA OS FILTROS DE INTERPOLAÇÃO DA ESTIMAÇÃO DE MOVIMENTO FRACIONÁRIA DO CODEC AV1

**DAIANE FONSECA FREITAS<sup>1</sup>; CLÁUDIO DINIZ<sup>2</sup>; MATEUS GRELLERT<sup>3</sup>;**

**GUILHERME CORRÊA<sup>4</sup>**

<sup>1</sup>*Universidade Federal de Pelotas – dffreitas@inf.ufpel.edu.br*

<sup>2</sup>*Universidade Federal do Rio Grande do Sul – cmdiniz@inf.ufrgs.br*

<sup>3</sup>*Universidade Federal do Rio Grande do Sul – mateusgrellert@gmail.com*

<sup>4</sup>*Universidade Federal de Pelotas – gcorrea@inf.ufpel.edu.br*

## 1. INTRODUÇÃO

Codificadores de vídeo eficientes são essenciais para transmitir e armazenar vídeos digitais em dispositivos eletrônicos modernos. No entanto, para alcançar uma elevada eficiência de codificação é necessário incorporar ferramentas avançadas no codificador, o que aumenta significativamente o custo computacional e o consumo de energia. Assim, a concepção de aceleradores de *hardware* eficientes em termos de energia para a codificação e decodificação de vídeo é essencial.

O codec isento de *royalties* AV1 (*AOMEDIA Video 1*), atinge taxas de compressão 30% superiores às dos codificadores anteriores, como o seu antecessor, o codec VP9, e o padrão *High Efficiency Video* (HEVC) (AOMEDIA, 2018). Para alcançar este objetivo, o principal custo computacional do AV1 reside na etapa de predição inter-quadros, que representa mais de 70% do tempo de execução do software de referência libaom (BENDER et al., 2023). Este fato deve-se à adição de novas ferramentas nessa etapa, como a *Overlapped Block Motion Compensation* (OBMC) e *Warped Motion Compensation* (WMC), bem como a adoção do esquema de filtragem adaptativa, que é aplicado à parte fracionária da estimação de movimento (ME), a estimação de movimento fracionária (FME), bem como à compensação de movimento (MC). Nesse esquema, o AV1 permite o uso de 75 filtros do tipo FIR (*Finite Impulse Response*) diferentes para a geração de amostras de pixels de posição fracionária (HAN et al., 2021). Esses filtros estão agrupados em três famílias com 15 filtros cada, chamadas Regular, Sharp e Smooth, além de versões aproximadas das famílias Regular e Smooth.

Dado o grande número de filtros envolvidos no processo de interpolação do AV1 e o fato de que os filtros de interpolação são fundamentais para o desempenho de um codificador de vídeo (MUKHERJEE et al., 2013), torna-se essencial adotar estratégias que reduzam essa complexidade, como o desenvolvimento de aceleradores de *hardware*, com especial atenção à eficiência energética. Com base nisso, este trabalho propõe um acelerador de hardware multiversão para o módulo de interpolação de amostras da FME do codec AV1, incorporando técnicas de redução de potência, computação aproximada e reaproveitamento de *hardware* comum entre versões precisas e aproximadas de cada família de filtros de interpolação do AV1.

## 2. METODOLOGIA

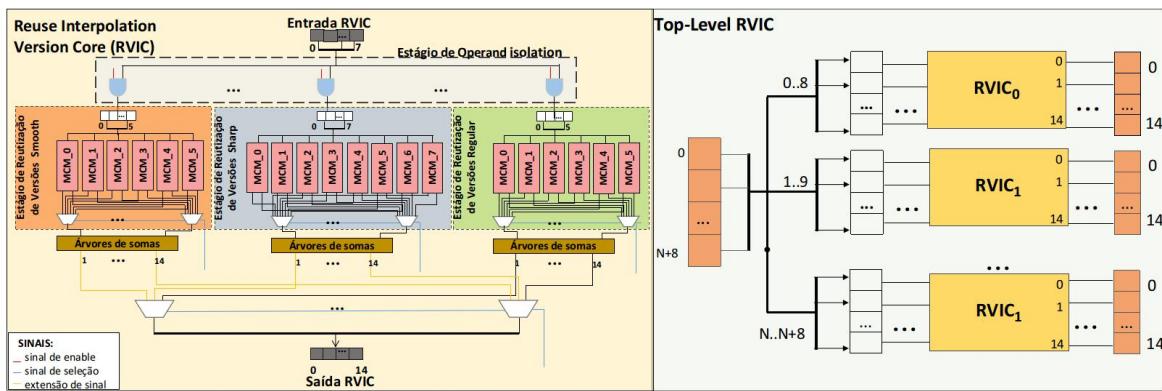

O acelerador de *hardware* proposto neste trabalho está representado na Figura 1. O projeto implementa três versões de cada filtro de interpolação (uma precisa, duas aproximadas) com reaproveitamento de *hardware* entre as versões aproximada e original das famílias de filtros de interpolação do codificador AV1 com o objetivo de

diminuir a área do circuito. Além disso, suporta o processo de interpolação adaptativa permitido no AV1 e emprega *operand isolation* para diminuir a dissipação de potência sempre que um tipo de filtro não é utilizado de acordo com diferentes cenários de codificação. A arquitetura nomeada *Reuse Interpolation Version Core* (RVIC), mostrada na Figura 1(a), apresenta três núcleos de processamento que descrevem os filtros de interpolação do esquema de filtragem adaptativa AV1. Essas unidades foram implementadas sem o uso de operadores de multiplicação, utilizando a abordagem *Multiple Constant Multiplication* (MCM) (VORONENKO; PÜSCHEL, 2007), e são identificadas como Estágios de Reutilização de Versões Regular, Sharp e Smooth.

Tendo em vista a eficiência computacional, foram também descritas duas propostas de versões aproximadas dos coeficientes fixos para cada família de filtros. Estas aproximações seguem a metodologia apresentada em FREITAS (2023), e podem ser adaptadas para processamento na etapa ME. A estratégia de aproximação adotada na versão Aproximada 1 consiste em permitir apenas um somador no caminho crítico dos dados nos MCMs. Logo, quando necessário são adicionados deslocamentos para que o novo coeficiente do filtro seja o mais próximo possível do coeficiente original. Na versão Aproximada 2, não há somadores no caminho crítico dos MCMs. Desse modo, o hardware do MCM é substituído por deslocamentos cujo valor mais se aproxima do valor original. Assim, dentro de cada unidade de processamento, estão disponíveis três versões possíveis para cada família de filtros.

A Figura 1(b) ilustra a estrutura *top-level* do projeto RVIC. A arquitetura foi concebida para processar blocos de  $4 \times 4$  amostras, já que blocos maiores podem ser processados a partir deste tamanho de bloco. A entrada do acelerador tem um paralelismo de 12 amostras. Este número foi definido considerando 4 pixels inteiros que constituem um bloco  $4 \times 4$ , mais 8 amostras para interpolação adequada dos pixels à esquerda e à direita do bloco a ser processado. Assim, para obter o número necessário de amostras para interpolar um bloco completo na saída do projeto *top-level*, são necessárias várias instâncias da estrutura RVIC. O processamento de um bloco completo demora 16 ciclos para a etapa MC e 51 ciclos para a etapa ME.

Figura 1: (a) Acelerador *Reuse Version Interpolation Core* (RVIC) e (b) arquitetura *top-level*, que recebe como entrada uma linha do bloco acrescida da zona de preenchimento ( $N+8$ ).

### 3. RESULTADOS E DISCUSSÃO

O acelerador de *hardware* foi descrito em VHDL (*Very High Speed Integrated Circuits Hardware Description Language*), sintetizado para tecnologia de célula padrão TSMC de 40nm, com 1,1V e 25°C usando a ferramenta Cadence RTL *Compilation tool*, e contagem de portas com base em NANDs 2. A potência foi estimada a partir de entradas reais. Ainda, a RVIC é um projeto configurável, onde

podem ser selecionados nove modos de funcionamento, logo foram realizadas nove sínteses. Os resultados apresentados na 6<sup>a</sup> coluna da Tabela 1 mostram que a frequência máxima de 833,3 MHz, a RVIC pode processar vídeos 8K a 50 fps no cenário MC e 2.656,14 milhões de amostras por segundo. De acordo com a configuração selecionada, a dissipação de potência varia de uma faixa de valores de 21,25 mW na configuração mais econômica até à configuração mais dispendiosa, com 40,06 mW.

Também podemos observar na Tabela 1 a comparação da RVIC com trabalhos relacionados. Quando comparado com a DOMANSKI et al., (2019), o projeto RVIC opera uma frequência 2,98× superior e requer uma área 3,48× maior. Quanto à resolução, ambos são capazes de processar vídeo de 4320p, mas o RVIC atinge uma taxa de quadros mais alta. Ademais, DOMANSKI et al., (2019) dissipava mais potência que a todas as configurações da RVIC. Comparada a DOMANSKI et al., (2021), a arquitetura RVIC funciona com frequência mais alta e atinge maior *throughput*. Em termos de dissipação de potência, como se trata de uma versão aproximada, apenas as seis versões aproximadas do RVIC foram comparadas. Assim, Domanski et al., (2021) requer uma menor dissipação de potência quando comparado com todas as versões da RVIC para os filtros Sharp, bem como com a configuração Aproximada 1 Regular. No entanto, comparada as versões Aproximada 2 Regular, Aproximada 1, e Aproximada 2 Smooth, a RVIC apresenta redução de potência de 0,89%, 7,69% e 20,69%, nessa ordem. Quando comparada a FREITAS et al., (2022), RVIC funciona a uma frequência mais baixa. Ainda assim, FREITAS et al.,(2022) é menos eficiente em termos energéticos do que todas as versões da RVIC. Por fim, em comparação a FREITAS et al., (2023), a RVIC também alcança resultados de dissipação de potência mais baixos em todas as suas configurações de operação.

Tabela 1: Resultados de síntese e comparação com trabalhos relacionados.

| Trabalhos Correlatos | DOMANSKI (2019)       | DOMANSKI (2021)      | FREITAS (2022)        | FREITAS (2023)             | RVIC                       |

|----------------------|-----------------------|----------------------|-----------------------|----------------------------|----------------------------|

| Famílias de Filtros  | Todos+Bil.<br>Preciso | Todos+Bil.<br>Aprox. | 3 famílias<br>Preciso | 3 famílias<br>Prec./Aprox. | 3 famílias<br>Prec./Aprox. |

| Tec. (nm)            | 40                    | 40                   | 40                    | 40                         | 40                         |

| Freq. (MHz)          | 279,9                 | 686,0                | 1000<br>833,3         | 833,3                      | 833,3                      |

| Portas (K)           | 141,10                | 72,64                | 324,79                | 473,01                     | 362,74                     |

| Potência (mW)        | 81,31                 | 26,79                | 51,15                 | 41,30                      | 21,25 a 40,06              |

| Resol. MC            | 4320p<br>@30qps       | 4320p<br>@30qps      | 4320p<br>@60qps       | 4320p<br>@50qps            | 4320p<br>@50qps            |

| Through.<br>(Mam./s) | -                     | -                    | 3.187,5               | 2.656,14                   | 2.656,14                   |

#### 4. CONCLUSÕES

Este artigo apresenta um acelerador de *hardware* eficiente para o módulo de interpolação de amostras FME/MC do codificador AV1, denominado *Reuse Interpolation Version Core* (RVIC). O foco principal do projeto é explorar, em diferentes níveis de abstração, o esquema adaptativo dos filtros de interpolação do AV1, com foco na eficiência energética para esta etapa dispendiosa do processo de codificação de vídeo. Portanto, o projeto proposto emprega a técnica *operand*

*isolation* para isolar operandos e famílias de filtros que não são utilizados durante o processo de interpolação, reduzindo a dissipação de potência dinâmica. A arquitetura foi desenvolvida utilizando multiplicações através de somas e deslocamentos, que são menos custosos em recursos de *hardware*. Além disso, foram propostas duas versões aproximadas das três famílias de filtros de interpolação definidas no AV1, totalizando nove configurações possíveis para o funcionamento da RVIC, que também usa reaproveitamento de *hardware* entre expressões comuns a diferentes versões do mesmo filtro, reduzindo ainda mais a área e a dissipação de potência. Para além disso, o acelerador RVIC apresenta melhores resultados de potência comparado aos trabalhos relacionados, sendo a única proposta configurável centrada nos filtros de interpolação FME/MC do codificador AV1.

Em trabalhos futuros exploraremos um modelo preditivo baseado em aprendizado de máquina para estimar a melhor combinação de filtros de interpolação para cada bloco.

## 5. REFERÊNCIAS BIBLIOGRÁFICAS

AOMEDIA. **AV1**. Online. Acessado em 20 de mar. 2021. Disponível em: <https://aomedia.org/av1-features/>

BENDER, I. et al. Complexity and compression efficiency analysis of libaom AV1 vídeo codec. **Journal of Real-Time Image Processing**, [S.I.], v.20, n.3, p.50, 2023.

DOMANSKI, R. et al. High-throughput multifilter interpolation architecture for AV1 motion compensation. **IEEE Transactions on Circuits and Systems II: Express Briefs**, v. 66, n. 5, p. 883-887, 2019.

DOMANSKI, R. et al. Low-power and high-throughput approximated architecture for AV1 FME interpolation. In: **2021 IEEE INTERNATIONAL SYMPOSIUM ON CIRCUITS AND SYSTEMS (ISCAS)**. IEEE, 2021. p. 1-5.

FREITAS, D.; GRELERT, M.; DINIZ, C. M.; CORREA, G. Multiversion Low-Power Hardware Accelerator for the AV1 Interpolation Filters. In: **2023 IEEE INTERNATIONAL SYMPOSIUM ON CIRCUITS AND SYSTEMS (ISCAS)**. IEEE 2023. 2023. p.1–5.

FREITAS, D. et al. High-Throughput Multifilter VLSI Design for the AV1 Fractional Motion Estimation. In: **SBC/SBMICRO/IEEE/ACM SYMPOSIUM ON INTEGRATED CIRCUITS AND SYSTEMS DESIGN (SBCCI)**, 2022., 2022. Anais. . . [S.I.: s.n.], 2022. p.1–6.

HAN, J. et al. A technical overview of AV1. **Proceedings of the IEEE**, v. 109, n. 9, p. 1435-1462, 2021.

MUKHERJEE, D. et al. A technical overview of VP9—the latest open-source video codec. In: **SMPTE 2013 Annual Technical Conference & Exhibition**. SMPTE, 2013. p. 1-17.

VORONENKO, Y.; PÜSCHEL, M.. Multiplierless multiple constant multiplication. **ACM Transactions on Algorithms (TALG)**, v. 3, n. 2, p. 11-es, 2007.