## **ANÁLISE DO IMPACTO DE UM EVENTO TRANSIENTE ÚNICO EM UMA PORTA LÓGICA NAND2 PLANAR CMOS**

**GUSTAVO R. NYGAARD<sup>1</sup>; HENRIQUE KESSLER<sup>2</sup>; LEOMAR DA ROSA JR.<sup>3</sup>**

<sup>1</sup>*Universidade Federal de Pelotas – grnygaard@inf.ufpel.edu.br*

<sup>2</sup>*Universidade Federal de Pelotas – hckessler@inf.ufpel.edu.br*

<sup>3</sup>*Universidade Federal de Pelotas – leomarjr@inf.ufpel.edu.br*

### **1. INTRODUÇÃO**

O avanço da microeletrônica proporcionou diversos benefícios para a tecnologia CMOS (Semicondutor de óxido de metal complementar), como a redução do tamanho dos transistores e consequentemente o aumento da velocidade dos dispositivos. No entanto, esta redução no tamanho dos transistores, combinada com uma menor tensão de alimentação e frequências operacionais maiores, diminuem a confiabilidade da tecnologia CMOS devido a sua susceptibilidade à radiação.

Quando partículas energéticas atingem o circuito integrado, existe a possibilidade de criar uma corrente elétrica momentânea com um perfil de dupla exponencial. Este pulso elétrico é conhecido como Evento Transiente Único (SET). Caso a partícula tenha energia suficiente, este evento pode alterar o estado de um bit de '1' para '0' ou de '0' para '1', resultando em um erro chamado de Evento de Falha Única (SEU).

Estes eventos são particularmente preocupantes em aplicações críticas, como por exemplo, aplicações aeroespaciais (satélites e aviões) e aplicações médicas. Portanto, compreender o comportamento dos SETs é fundamental para a compreensão do seu impacto em dispositivos CMOS e para desenvolver técnicas de mitigação eficazes e aumentar a confiabilidade de aplicações críticas.

Este trabalho tem como objetivo estudar o impacto de partículas ao interagirem com portas lógicas combinacionais através de simulação elétrica (SPICE). Buscando avaliar a resposta do circuito variando as condições em que a porta lógica se encontra, como diferentes valores de capacitância na saída e partículas com mais energia.

### **2. METODOLOGIA**

Para analisar o efeito causado pelas partículas ao interagirem com portas lógicas combinacionais, utilizou-se o programa LTSPICE para realizar simulações elétricas na tecnologia de 45nm PTM (Modelo de tecnologia preditiva), na variante de alto desempenho (HP). As simulações foram projetadas para observar o comportamento da porta lógica NAND2 em seus diferentes estados, considerando variadas capacidades de 2 fF, 10 fF e 20 fF.

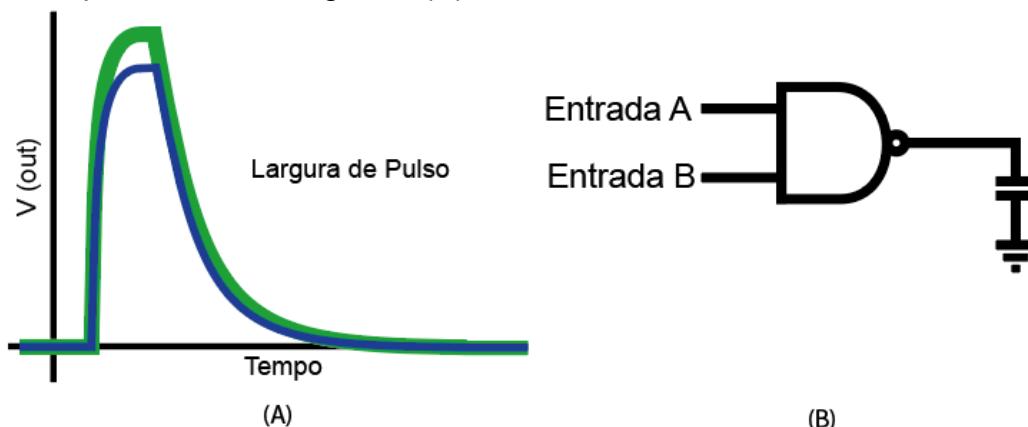

As partículas foram modeladas como fontes de corrente, seguindo uma função exponencial (MESSENGER, 1982). O comportamento dessa corrente se caracteriza por um aumento exponencial de 0 µA para 640 µA ou 720 µA, com uma constante de tempo de subida de 2 ps. Após atingir o valor máximo, a corrente decai exponencialmente, seguindo uma curva de descarga com constante de tempo de 10 ps. Esse comportamento resulta em uma forma de onda com perfil de dupla exponencial, o que permite a extração da duração

(largura do pulso) da partícula como mostrado na Figura 1 (A) sob a porta lógica NAND2 representada na Figura 1 (B).

Figura 1: (A) Formato da corrente injetada no circuito. (B) Representação visual do ambiente de simulação.

Para configurar o ambiente de simulação a porta lógica NAND2 foi inicialmente projetada utilizando a ferramenta SwitchCraft (CALLEGARO, 2010), para extração do SPICE Netlist, que é uma representação textual detalhada do circuito eletrônico, o Netlist fornece uma descrição abrangente dos componentes do circuito, incluindo resistores, capacitores, transistores, além de fontes de tensão e corrente. A porta lógica foi dimensionada seguindo a técnica do *Logical Effort* (SUTHERLAND, 1999) que é uma técnica usada para analisar e otimizar o desempenho de circuitos digitais em tecnologia CMOS, onde o L (Comprimento de canal do transistor) utilizado é de 50 n, o W (Largura do canal do transistor) utilizado é de 100 n, e o fator de proporção relacionado com o dimensionamento relativo entre transistores NMOS e PMOS nas portas lógicas utilizado é de 1,5.

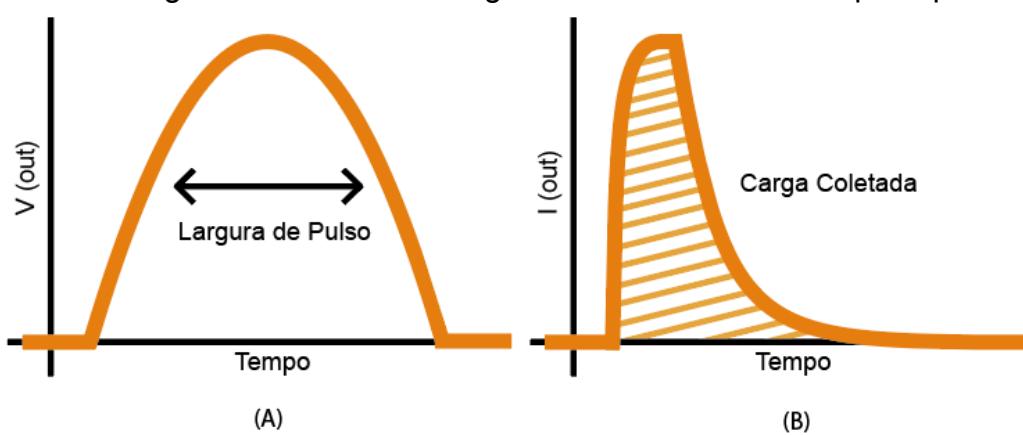

Dessa forma, descreve-se os comandos para extrair as medidas da largura de pulso Figura 2 (A) gerado pelo SET, ou seja, a duração do pulso de tensão induzido pela partícula no circuito. O comando mede o intervalo de tempo entre dois eventos, o primeiro ocorre quando a tensão de saída ( $v(\text{out})$ ) passa da metade do valor da fonte de alimentação, enquanto o segundo evento acontece quando a tensão cai para menos da metade do valor da fonte de alimentação. O segundo comando mede a carga coletada demonstrada na Figura 2 (B), calculando a integral da corrente ao longo de um intervalo de tempo específico.

Figura 2: (A) Formato da tensão de um SET. (B) Representação visual da integral da carga coletada.

### 3. RESULTADOS E DISCUSSÃO

A Tabela 1 apresenta os resultados obtidos nas simulações elétricas para a largura de pulso SET com todas as combinações de entrada, capacidade e pico de corrente da dupla exponencial.

Tabela 1: Resultados obtidos para largura do pulso com as duas partículas nas simulações elétricas na porta lógica NAND com capacidades diferentes.

| Porta Lógica | Capacitância   |                |                |                |                |                |

|--------------|----------------|----------------|----------------|----------------|----------------|----------------|

|              | 2 fF           |                | 10 fF          |                | 20 fF          |                |

|              | Pico Dupla Exp |

| Entrada      | 640 µA         | 720 µA         | 640 µA         | 720 µA         | 640 µA         | 720 µA         |

| 00           | 41,6 ps        | 43,2 ps        | 45,3 ps        | 54,7 ps        | 0,0 ps         | 23,0 ps        |

| 01           | 65,0 ps        | 66,5 ps        | 94,0 ps        | 110,0 ps       | 38,8 ps        | 62,4 ps        |

| 10           | 59,8 ps        | 61,2 ps        | 94,7 ps        | 111,0 ps       | 40,4 ps        | 63,8 ps        |

| 11           | 56,0 ps        | 57,5 ps        | 75,8 ps        | 91,1 ps        | 23,8 ps        | 45,8 ps        |

Analizando a Tabela 1, observa-se que em todos os estados avaliados a duração da largura do pulso é maior na partícula de 720 µA, em comparação com a de 640 µA. Esta diferença pode ser atribuída à maior quantidade de energia depositada, que, ao impactar a porta lógica, gera uma corrente elétrica mais intensa. Como resultado, a porta lógica leva mais tempo para corrigir o erro induzido por essa partícula, refletindo um aumento no tempo necessário para restaurar o estado original do circuito.

Quando uma partícula atinge uma porta lógica, isto resulta na injeção de corrente no nó atingido. Quanto maior a capacidade deste nó, maior a carga necessária para causar um SET. Assim, aumentar a capacidade torna mais difícil que um impacto de partícula provoque uma alteração no estado da porta lógica, como apresentado na Tabela 1 entre a capacidade 2 fF e 20 fF, o aumento da capacidade faz com que a largura do pulso seja menor, devido a corrente induzida pela partícula ser a mesma.

No entanto, no caso de capacidade 2 fF com entradas '00' e com a partícula 640 µA não alcançou energia suficiente para causar um SET, ocorrendo um mascaramento elétrico. Isto ocorre quando o pulso é afetado pelas propriedades elétricas e capacidades das portas lógicas em seu caminho de propagação, a magnitude ou a duração do SET pode diminuir de modo que não seja mais suficiente para atingir próximo estágio lógico. Neste caso devido os dois transistores PMOS estarem ligados a correção da porta lógica é mais intensa que a carga coletada da partícula.

Podemos observar na Tabela 1 que nos estados '01' e '10' possui um aumento significativo na largura de pulso em comparação ao estados '00' e '11', isto ocorre devido a própria porta lógica restaurar o estado original do circuito, ou seja, ela é responsável por corrigir o erro. Na porta lógica NAND2, quando uma

carga é induzida no dreno do transistor NMOS, é gerado um pulso de tensão que temporariamente altera o valor de saída para '0'. Como apenas um transistor PMOS está ativo nos estados '01' e '10' este é responsável por restaurar o valor correto da saída ('1'). A largura de pulso nos estados '00' e '11' diminui quando comparado aos estados '01' e '10' o tempo necessário para restaurar o estado correto do circuito por possuir dois transistores realizando esta restauração.

Observando a Tabela 2, ao variar a capacidade da porta lógica não foi observada mudanças na carga coletada, pois alterações no circuito causam impacto na duração do erro, não na carga coletada pela partícula.

Tabela 2: Resultados obtidos para carga coletada com as duas partículas nas simulações elétricas na porta lógica NAND2 com capacidades diferentes.

|              | Pico Dupla Exp |         |

|--------------|----------------|---------|

| Capacitância | 640 µA         | 720 µA  |

| 2 fF         | 14,7 fF        | 16,5 fF |

| 10 fF        | 14,7 fF        | 16,5 fF |

| 20 fF        | 14,7 fF        | 16,5 fF |

#### 4. CONCLUSÕES

Neste trabalho analisou-se o impacto de partículas energéticas na porta lógica NAND2 variando as condições em que a porta lógica se encontra, como diferentes valores de capacidade na saída buscando avaliar a resposta do circuito por meio de simulações elétricas. Os resultados demonstraram que partículas de 720 µA geram pulsos SET mais longos do que partículas de 640 µA, devido à maior energia. O aumento da capacidade nas portas lógicas dificulta a ocorrência de SETs, podendo evitar a sua ocorrência, devido a carga necessária para causar uma alteração no estado do circuito ser maior.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

CALLEGARO, V. et al. SwitchCraft: a framework for transistor network design. In: **Proc. of the 23rd symp. on Integrated circuits and system design**. 2010. p. 49-53.

SUTHERLAND, I. et al. **Logical effort: designing fast CMOS circuits**. Morgan Kaufmann, 1999.

MESSENGER, G. C. "Collection of charge on junction nodes from ion tracks." **IEEE Transactions on nuclear science** **29.6** (1982): 2024-2031.