## AVALIAÇÃO DO ARMAZENAMENTO APROXIMADO NA PREDIÇÃO INTRA-QUADROS EM CODIFICADORES VVC

YASMIN SOUZA CAMARGO<sup>1</sup>; BRUNO ZATT<sup>1</sup>;

DANIEL MUNARI VILCHEZ PALOMINO<sup>1</sup>; FELIPE MARTIN SAMPAIO<sup>2</sup>

<sup>1</sup> Universidade Federal de Pelotas (UFPel) – {yasmin.sc, zatt, dpalomino}@inf.ufpel.edu.br

<sup>2</sup> Instituto Federal do Rio Grande do Sul (IFRS) – felipe.sampaio@farroupilha.ifrs.edu.br

### 1. INTRODUÇÃO

O tráfego de vídeo está em crescimento contínuo e representa uma parte significativa dos dados móveis globais, com projeções de que chegará a 76% até 2029 (JONSSON et al., 2024). Isso aumenta a importância da eficiência na codificação de vídeo, especialmente para dispositivos móveis que são aparelhos com limitações de autonomia da bateria. O Versatile Video Coding (VVC) é o padrão atual de compressão de vídeo, oferecendo 50% de melhoria na taxa de compressão comparado ao seu antecessor o HEVC, mas com um grande aumento de complexidade computacional. Um dos maiores desafios no VVC é a predição intra-quadro, responsável por 29% do processamento total e até 108 vezes mais complexa do que em padrões anteriores (SIQUEIRA et al., 2020). Nesse contexto, torna-se essencial explorar oportunidades de pesquisa focadas no baixo consumo de energia, com especial atenção aos pontos críticos de complexidade, como o módulo de predição intra-quadro. Uma abordagem para reduzir o consumo de energia é o uso de técnicas de armazenamento aproximado que são ideais para tarefas intensivas em memória e computacionalmente exigentes, como é o caso da codificação de vídeo (SAMPAIO et al., 2015). No armazenamento aproximado, a redução do consumo de energia pode ser alcançada, por exemplo, através da diminuição da tensão de alimentação da memória, resultando em erros durante as operações de leitura e escrita da memória que, consequentemente, degradam a qualidade do vídeo codificado (FRUSTACI et al., 2015). O principal objetivo deste trabalho é explorar o armazenamento aproximado na predição intra-quadro no VVC e analisar o equilíbrio entre as perdas de eficiência de codificação e a redução do consumo de energia.

### 2. PREDIÇÃO INTRA-QUADROS E MODELO DE MEMÓRIA

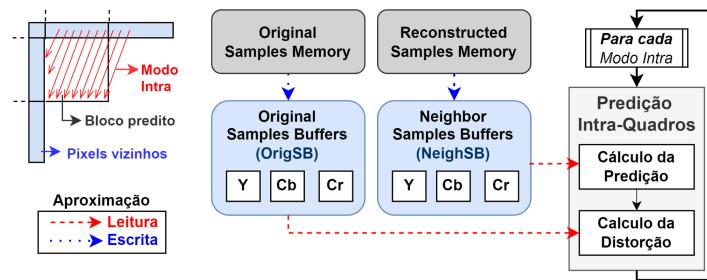

A predição intra-quadro em um codificador de vídeo visa reduzir a redundância espacial dentro do quadro. O fluxo de execução e as memórias no qual o armazenamento aproximado foi analisado podem ser observados em azul na Figura 1. O processo começa, para cada bloco, com o Cálculo da Predição, onde são estimados os valores dos pixels de um bloco com base nas amostras armazenadas no Buffer de Amostras Vizinhas (*Neighbor Samples Buffer* - NeighSB), que contém dados dos blocos adjacentes. Em seguida, o Cálculo da Distorção avalia a qualidade dessas predições comparando-as com as amostras do vídeo original, armazenadas no Buffer de Amostras Originais (*Original Samples Buffer* - OrigSB). Esta comparação permite escolher a melhor correspondência entre a predição e o bloco original.

**Figura 1.** Modelo de memória da predição intra-quadro.

### 3. METODOLOGIA

Para gerar o perfil de resiliência a erros e avaliar o impacto do armazenamento aproximado nas memórias NeighSB e OrigSB da predição intra-quadro, simulamos erros de memória usando o framework Intel Pin (LEVI, 2005) com codificador VVC (WIECKOWSKI, 2021). A análise foi feita nos primeiros 17 quadros de quatro sequências de vídeo da Classe C (resolução 832x480 pixels), sendo elas *BasketballDrill*, *BQMall*, *RaceHorses* e *PartyScene*. Os experimentos foram realizados para valores do parâmetro de quantização (QP) de 22, 27, 32 e 37, conforme condições de teste padronizadas pelo VVC. O estudo foi conduzido em dois lotes: o primeiro para construir o perfil de resiliência com diferentes taxas de erro de  $10^{-2}$  a  $10^{-6}$  em configurações de codificador Random Access (RA) e All Intra (AI). O segundo lote avaliou comportamentos de erro para níveis de tensão de fornecimento em memória (0,55V, 0,6V e 0,7V) (FRUSTACI, 2015). De forma a minimizar os efeitos da aleatoriedade na avaliação dos erros de leitura e escrita, cada experimento foi repetido 30 vezes. Além disso, foram considerados os 10 bits como a largura dos dados para avaliação dos erros. A eficiência da codificação foi medida utilizando o BD-Rate, sendo este uma métrica de eficiência de codificação, sendo uma relação entre taxa de compressão e qualidade visual do vídeo codificado.

### 4. RESULTADOS E DISCUSSÃO

Esta seção apresenta análises e discussões sobre os resultados obtidos em relação ao perfil de resiliência do codificador VVC para uma ampla gama de BERs e parâmetros (Item 4.1), e a economia no consumo de energia da memória para exploração aproximada do armazenamento (Item 4.2).

#### 4.1. PERFIL DE RESILIÊNCIA DO CODIFICADOR DO VVC

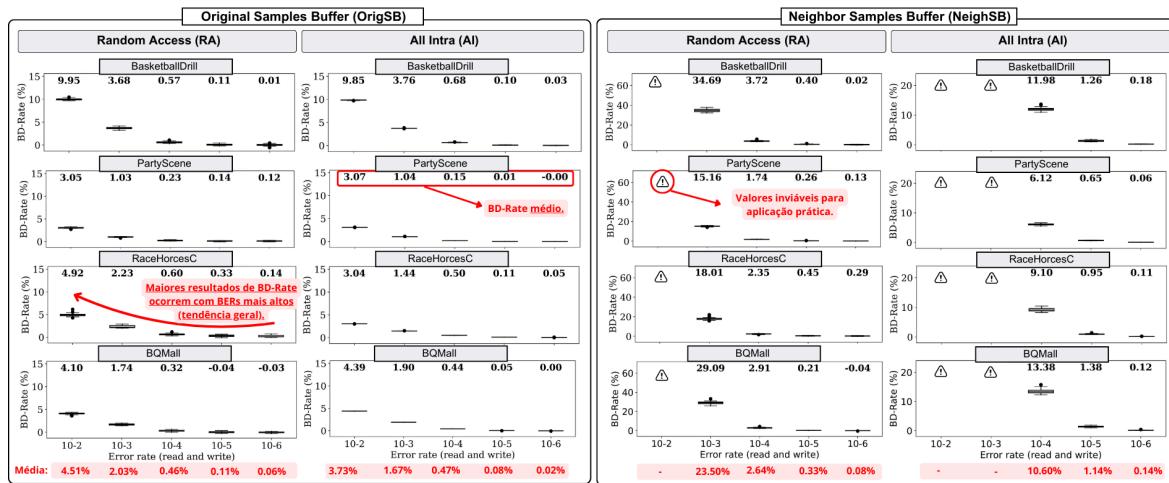

A Figura 2 apresenta gráficos do tipo *boxplot* ilustrando os perfis de resiliência a erros das memórias aproximadas na predição intra-quadro (OrigSB e NeighSB). Os gráficos comparam o impacto dos erros de memória na BD-Rate para todas as sequências de vídeo avaliadas. Cada gráfico relaciona as taxas de erro de bit (BERs, de  $10^{-6}$  a  $10^{-2}$ ) nas operações de leitura e escrita de memória com os valores correspondentes de BD-Rate. Os resultados mostram que à medida que mais erros são introduzidos, observa-se um aumento correspondente nos valores de BD-Rate. Além disso, devido a características únicas de cada vídeo, cada sequência apresenta resultados variados.

Figura 2. Resultados de BD-Rate (%) para as taxas de erro.

Valores maiores que 40% de BD-Rate são indicados pelo ponto de exclamação na Figura 2, representando uma degradação significativa na qualidade do vídeo e nas taxas de compressão alcançadas. Estes símbolos são encontrados na memória NeighSB, sendo considerada, portanto, uma memória pouco resiliente, tornando a sua utilização inviável no contexto deste trabalho. Além disso, pode-se observar que a configuração AI maximiza a influência dos erros de acesso à memória. Esse comportamento é esperado uma vez que no modo AI a predição intra-quadro é aplicada a todos os blocos, maximizando a influência dos erros de acesso à memória.

Em contraste, OrigSB apresenta resultados promissores com níveis de tolerância mais altos: os resultados de BD-Rate alcançam no pior caso 9,9% e 3,7%, para configuração RA para as taxas  $10^{-2}$  e  $10^{-3}$  respectivamente. Essas diferenças significativas nos valores podem ser explicadas pela natureza da exploração da aproximação nessas memórias: enquanto que a aproximação em OrigSB afeta apenas a etapa de Cálculo de Distorção, erros nas operações em NeighSB acabam por se propagar para as etapas restantes do codificador.

#### 4.2. EXPLORAÇÃO DO ARMAZENAMENTO APROXIMADO

A Tabela 1 resume os resultados de BD-Rate,  $\Delta$ PSNR,  $\Delta$ BR e economia de energia para diferentes níveis de operação SRAM (0,55 V, 0,6 V e 0,7 V) com foco na configuração de RA, pois na prática é o padrão utilizado para a maioria das aplicações de codificação de vídeo.

| Módulo de memória | Métricas de avaliação | Nível de operação      |       |        |

|-------------------|-----------------------|------------------------|-------|--------|

|                   |                       | 0,7V                   | 0,6V  | 0,55V  |

| OrigSB            | BD-Rate [%]           | 1,04                   | 2,34  | 4,23   |

|                   | $\Delta$ BR [%]       | 0,90                   | 2,70  | 5,30   |

|                   | $\Delta$ PSNR [dB]    | -0,02                  | -0,05 | -0,08  |

|                   | Red. En. Din. [%]     | 36,40                  | 54,37 | 58,25  |

|                   | Aces. Mem. [ $10^6$ ] | 1,83 (3,6x vs NeighSB) |       |        |

| NeighSB           | BD-Rate [%]           | 15,43                  | >40   | >40    |

|                   | $\Delta$ BR [%]       | 8,80                   | 62,60 | 83,70  |

|                   | $\Delta$ PSNR [dB]    | 15,43                  | 80,29 | 108,86 |

|                   | Red. En. Din. [%]     | 34,03                  | 52,88 | 56,93  |

|                   | Aces. Mem. [ $10^6$ ] | 0,51                   |       |        |

Tabela 1. Exploração de armazenamento aproximado para memória SRAM.

Para OrigSB, as perdas médias de qualidade são pequenas (até 0,07 dB) com reduções significativas de energia dinâmica variando de 36% a 58%. Como consequência, ocorre um aumento de BD-Rate de 1%-4,2%, levando a valores máximos de  $\Delta$ PSNR e  $\Delta$ BR de -0,08 e 5,3%, respectivamente. As reduções de energia alcançadas em OrigSB representam um fator de 3,6x do que aquelas verificadas no NeighSB. Embora a exploração do armazenamento aproximado no NeighSB tenha alcançado economias de energia promissoras (34%-56%), a propagação dos erros de leitura/escrita impacta significativamente toda a eficiência de codificação do VVC, ao operar sob as taxas de erro SRAM adotadas: atingindo até 83,7% e -1,45 de quedas de taxa de bits e PSNR.

#### 4. CONCLUSÕES

Este artigo avaliou o armazenamento aproximado no codificador VVC, com foco nas regiões de memória para previsão intra-quadro para armazenar amostras originais e vizinhas. Inicialmente, analisamos uma ampla gama de taxas de erro em diferentes cenários de teste. Em seguida, consideramos taxas de erro realistas baseadas em níveis de operação de SRAM aproximada. Geralmente, observamos que o aumento das taxas de erro leva a maiores perdas na eficiência de codificação, com impactos variados em diferentes vídeos. A memória OrigSB demonstrou maior tolerância a erros, com perdas mínimas na qualidade do vídeo e na eficiência de codificação, mesmo nas maiores taxas de erro analisadas. Além disso, apresentou um potencial significativo para economias de energia, indicando propriedades promissoras para armazenamento aproximado. Em contraste, a memória NeighSB mostrou uma resiliência significativamente menor, com aumentos substanciais na BD-Rate e deterioração notável na qualidade do vídeo nas maiores taxas de erro avaliadas. A partir desses insights, o desafio que resta é otimizar o equilíbrio entre resiliência a erros, eficiência de codificação e eficiência energética, tornando a solução mais inteligente e eficaz para aplicações do mundo real.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

- FRUSTACI, F.; KHAYATZADEH, M.; BLAAUW, D.; SYLVESTER, D.; ALIOTO, M. **SRAM for error-tolerant applications with dynamic energy-quality management in 28 nm CMOS**. IEEE Journal of Solid-State Circuits, v.50, n.5, p. 1310–1323, 2015.

- JONSSON, P.; CERWALL, P.; UNDVALL, A.; KOCH, D. A.; DAVIS, S. **Ericsson mobility report**, Nov 2023.

- LEVI, O. **PIN: A dynamic binary instrumentation tool**. Tech. Rep., Intel Corporation, 2005.

- SAMPAIO, F.; SHAFIQUE, M.; ZATT, B.; BAMPI, S.; HENKEL, J. **Approximation-aware multi-level cells STT-RAM cache architecture**. In: INTERNATIONAL CONFERENCE ON COMPILERS, ARCHITECTURE AND SYNTHESIS FOR EMBEDDED SYSTEMS (CASES), 2015. p. 79–88.

- SIQUEIRA, I.; CORREA, G.; GRELLERT, M. **Rate-distortion and complexity comparison of HEVC and VVC video encoders**. In: IEEE LATIN AMERICAN SYMPOSIUM ON CIRCUITS & SYSTEMS (LASCAS), 11., 2020, 2020. p. 1–4.

- WIECKOWSKI, A. et al. **VVENC: An open and optimized VVC encoder implementation**. In: IEEE International Conference on Multimedia and Expo Workshops (ICMEW), 2021, p. 1–2.