## ABORDAGEM MCM PARA AS TRANSFORMADAS DST-VII E DCT-VIII PADRÃO VVC

**FRANKLIN SALES DE OLIVEIRA<sup>1</sup>; ANDRÉ MARCELO COELHO DA SILVA<sup>2</sup>;**

**LUCIANO VOLCAN AGOSTINI<sup>3</sup>**

<sup>1</sup>Universidade Federal de Pelotas – [fsoliveira@inf.ufpel.edu.br](mailto:fsoliveira@inf.ufpel.edu.br)

<sup>2</sup>Universidade Federal de Pelotas – [amcdsilva@inf.ufpel.edu.br](mailto:amcdsilva@inf.ufpel.edu.br)

<sup>3</sup>Universidade Federal de Pelotas – [agostini@inf.ufpel.edu.br](mailto:agostini@inf.ufpel.edu.br)

### 1. INTRODUÇÃO

Os vídeos digitais desempenham um papel muito importante na sociedade contemporânea, abrangendo áreas que vão desde comunicação eficaz até entretenimento e educação acessível. A pandemia da Covid-19 evidenciou esta importância. Um exemplo é o comércio de dispositivos eletrônicos, como smart TVs, smartphones e computadores, que teve um crescimento de 68% somente no ano de 2020. Também houve um crescimento no número de domicílios com conexão a internet, atingindo a marca de 61,8 milhões (AGÊNCIA BRASIL, 2020).

Com tantos aparelhos eletrônicos que utilizam vídeos com resolução cada vez mais elevada, existe a necessidade de técnicas de compressão de vídeo mais eficientes. Para contextualizar, comprimir vídeos é reduzir o número de bits necessários para representar o vídeo com pouco ou nenhum impacto na qualidade visual. Este esforço é justificável pois um vídeo não comprimido utiliza uma quantidade de bits muito elevada e isso impacta diretamente no armazenamento e na transmissão do próprio vídeo (AGOSTINI, 2007, p. 25):

Para armazenar uma sequência de curta duração, com 10 minutos, seriam necessários quase 19 bilhões de bytes (19GB). Para vídeos com resolução de 1920x1080 pixels a 30 quadros por segundo (usado em televisão digital com alta definição ou HDTV), com 24 bits por pixel, a taxa de transmissão sobe para 1,5 bilhões de bits por segundo (1,5 Gbps) e seriam necessários 112 bilhões de bytes (112 GB) para armazenar um vídeo com 10 minutos.

Não por acaso, no ano de 2020, foi lançado o padrão *Versatile Video Coding* (VVC), definido pelas equipes da ITU-T e da ISO. O VVC representa um avanço significativo em relação ao padrão anterior, o *High-Efficiency Video Coding* (HEVC). O VVC atinge o dobro da eficiência de codificação do HEVC, fornecendo a mesma qualidade visual com metade do número de bits (SILVA, 2023).

Segundo Bross *et al* (2021), o padrão VVC foi desenvolvido não apenas para proporcionar a redução substancial da taxa de bits em comparação aos seus antecessores, mas também para ser altamente versátil, ou seja, para cobrir todas as necessidades de mídias atuais e emergentes. Portanto, isso inclui vídeos com resoluções mais elevadas (8k ou maior), com tecnologias como HDR e WCG e com outros formatos, como vídeo 360° com foco em imersiva e realidade aumentada.

O VVC traz muitas novidades em todas as etapas da codificação, incluindo as etapas de predição intra-quadro e inter-quadros, transformadas diretas e inversas, quantização direta e inversa, codificação de entropia e filtros de laço. O

VCC também traz uma nova estrutura altamente flexível de particionamento dos quadros, chamada de árvore quaternária com árvore de múltiplos tamanhos aninhada (do inglês quadtree with nested multi-type tree - QTMT) (BROSS, 2021). Este trabalho está focado nas novas transformadas do VVC, incluindo a Transformada Discreta de Seno VII (DST-VII) e Transformada Discreta de Cosseno VII (DCT-VIII), que foram adicionadas à DCT-II convencional. As transformadas na codificação de vídeo permitem transformar a informação dos quadros do vídeo do domínio espacial para o domínio das frequências, onde técnicas avançadas de codificação removem ou atenuam as frequências que são menos relevantes para o sistema visual humano, permitindo que sejam atingidas elevadas taxas de compressão (AGOSTINI, 2007).

Este trabalho visa apresentar resultados de pesquisa desenvolvida para investigar os efeitos do uso de técnicas de Múltiplas Multiplicações por Constante (do inglês *Multiple Constant Multiplication* - MCM) quando aplicadas no projeto de hardware para as novas transformadas do VVC. A ideia das técnicas de MCM é eliminar o uso de multiplicadores convencionais, que são muito custosos, por somas e/ou subtrações de deslocamentos.

## 2. METODOLOGIA

A investigação apresentada neste trabalho considera quatro abordagens de MCM: Recodificação Baseada em Dígito (do inglês *Digit Based Recording* - DBR), DBR com Dígito Canônico com Sinal (do inglês *Canonical Signed Digit* - CSD), Grafo de Somador Reduzido n-Dimensional (do inglês *n-Dimensional Reduced Adder Graph* - RAG-n), e Heurística de Benefício Cumulativo (do inglês *Cumulative Benefit Heuristic* - Hcub).

Inicialmente, as somas e/ou subtrações por deslocamento para cada uma das abordagens MCM foram geradas pela ferramenta Spiral\* (<http://spiral.net/index.html>) para as constantes alvo necessárias para o cálculo da DST-VII e DCT-VIII de tamanho 4x4, que foram 29, 55, 74 e 84 em suas representações positivas ou negativas.

A seguir, foram projetadas e descritas arquiteturas em VHDL para as estas transformadas 4x4, seguidas de síntese visando FPGAs da Altera. A síntese usou a ferramenta Quartus II e o dispositivo alvo foi da família Cyclone V.

Uma das arquiteturas se baseia exclusivamente na combinação de somadores e deslocadores, ao passo que as três demais incluem, adicionalmente, subtratores, além de somadores e deslocamentos. Essas estruturas são designadas como Unidades de Multiplicação por Constantes (MCUs) e as MCUs podem realizar todas as multiplicações necessárias para calcular as transformadas 4x4.

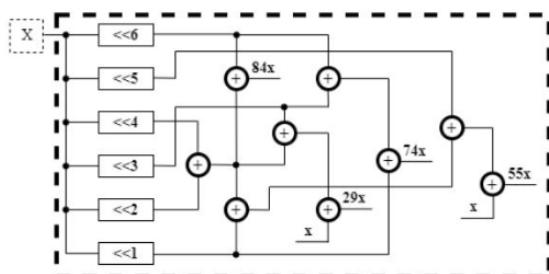

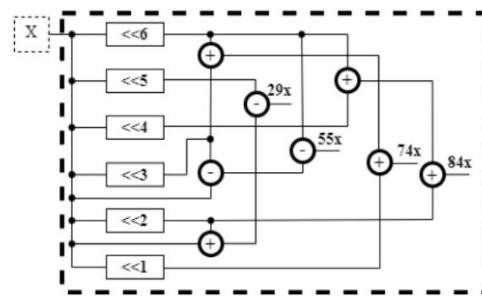

A primeira arquitetura explora a técnica DBR de MCM, que decompõe os coeficientes em somadores e deslocamentos e está apresentada na Figura 1. Porém, considerando que esta abordagem utiliza um número relativamente grande de somadores, uma outra versão DBR foi proposta, empregando duas constantes na representação binária e duas na representação CSD. A segunda solução está apresentada na Figura 2 (SILVA, 2023).

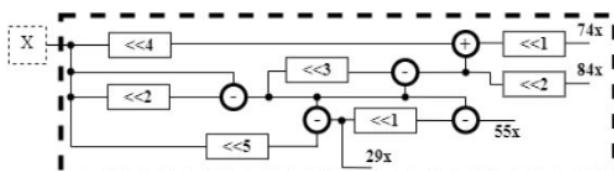

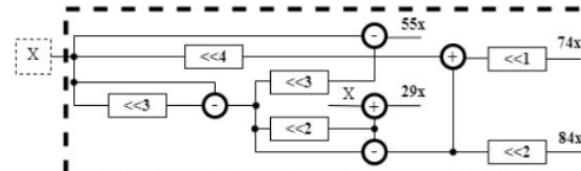

Também foram investigadas soluções de MCM baseadas em grafos, através dos algoritmos RAG-n e Hcub, visando obter melhores resultados. A solução gerada com RAG-n está apresentada na Figura 3, enquanto a Figura 4 apresenta a solução com Hcub.

Nas figuras das arquiteturas, os círculos indicam as operações de soma ou subtração, de acordo com o sinal apresentado em seu interior. Por outro lado, os retângulos apresentam as operações de deslocamento à esquerda, simbolizados por “ $<<$ ”. O número após o símbolo indica o número de bits que são deslocados. O deslocamento à esquerda equivale à multiplicação do número de entrada por uma potência de dois, definida pelo número de bits deslocados. Deste modo, “ $x << 3$ ” equivale a “ $x * 2^3$ ”, ou seja, equivale a “ $8x$ ”. As composições das operações do número de entrada “ $x$ ” para gerar cada uma das multiplicações por constantes também estão apresentadas nas figuras. A partir destas figuras é possível perceber que as multiplicações por constantes podem ser obtidas a partir de diferentes combinações de somas e/ou subtrações de deslocamentos.

Figura 1. Arquitetura DBR

Figura 2. Arquitetura DBR-CSD

Figura 3. Arquitetura RAG-n

Figura 4. Arquitetura Hcub

### 3. RESULTADOS E DISCUSSÃO

Os resultados para as quatro soluções arquiteturais sem multiplicadores para as novas transformadas do VVC, a DST-VII e a DCT-VIII, são discutidos nesta seção. A Tabela 1 apresenta a quantidade de recursos de hardware necessários para cada solução, incluindo deslocadores, somadores e subtratores. Também foram incluídos os resultados da síntese do hardware para FPGAs Altera, considerando o número de módulos de lógica adaptativa (do inglês *adaptive logic module* - ALM) necessários em cada caso.

De acordo com os resultados apresentados na Tabela 1, as abordagens MCM que utilizam menos recursos de hardware são as abordagens baseadas em grafos, ou seja, RAG-n e Hcub. Nestes casos, são necessários cinco somadores ou subtratores e sete deslocamentos. Mesmo com um deslocamento a mais do que as soluções DBR, as soluções RAG-n e Hcub usam um número muito menor de somadores e subtratores e, como estes são elementos mais custos em hardware do que os deslocadores, o uso de hardware em termos de ALMs do FPGA alvo são significativamente menores no caso das soluções RAG-n e Hcub.

Entre as soluções DBR, ficou claro o benefício do uso de CSD, uma vez que é usado um operador aritmético a menos, mantendo o número de deslocamentos, implicando em uma redução do uso de ALMs do FPGA alvo.

| Recurso       | DBR | DBR-CSD | RAG-n | Hcub |

|---------------|-----|---------|-------|------|

| Deslocamentos | 6   | 6       | 7     | 7    |

| Somadores     | 9   | 5       | 1     | 2    |

| Subtratores   | 0   | 3       | 4     | 3    |

| ALMs          | 52  | 41      | 32    | 32   |

Tabela 1. Resultados

#### 4. CONCLUSÕES

Os resultados obtidos com esse trabalho mostram que a arquitetura que usa MCM baseada em grafos (RAG-n e Hcub) reduz a quantidade de recursos de hardware necessários na implementação das arquiteturas da DST-VII 4x4 e da DCT-VIII 4x4 do VVC. A redução no uso de recursos de hardware implica, também, em um menor consumo de energia, o que é muito importante, principalmente para dispositivos alimentados por bateria.

Assim, as transformadas para tamanhos de blocos maiores que 4x4 serão desenvolvidas em trabalhos futuros usando uma das duas soluções MCM baseadas em grafos.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

AGOSTINI, L. V. **Desenvolvimento de Arquiteturas de Altas Desempenho Dedicadas à Compressão de Vídeo Segundo o Padrão H.264/AVC.** 2007. 172f. Tese (Doutorado em Ciência da Computação) - Curso de Pós-graduação em Computação, Universidade Federal do Rio Grande do Sul.

ALVARENGA, D. **Com pandemia, comércio eletrônico tem salto em 2020 e dobra participação no varejo.** G1, 26 fev. 2021.

Acesso em: 20 set. 2023. Online. Disponível em: <https://g1.globo.com/economia/noticia/2021/02/26/com-pandemia-comercio-elettronico-tem-salto-em-2020-e-dobra-participacao-no-varejo-brasileiro.ghtml>

BROSS, B. et al. . Overview of the Versatile Video Coding (VVC) Standard and Its Applications. **IEEE transactions on circuits and systems for video technology.** vol. 31, n. 10, october 2021. Acesso em: 20 set. 2023. Online. Disponível em: <https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=9503377> <https://ieeexplore.ieee.org/abstract/document/9503377>

SILVA, A. M C. et at. Multiplierless Design Space Exploration for the 4x4 DST-VII and DCT-VII VVC Transforms. **LASAS 2024.** (artigo submetido)

NITAHARA, A. **Estudo mostra que pandemia intensificou uso das tecnologias digitais,** Agência Brasil, Rio de Janeiro, 25 nov. 2021. Acesso em: 03 set. 2023. Online. Disponível em: <https://agenciabrasil.ebc.com.br/geral/noticia/2021-11/estudo-mostra-que-pandemia-intensificou-uso-das-tecnologias-digitais>