## DIMENSIONAMENTO ASSIMÉTRICO DE TRANSISTORES CMOS: UMA ABORDAGEM DIRECIONADA ÀS PORTAS COMPLEXAS

VÍTOR DE MELO MANDOWSKI<sup>1</sup>; HENRIQUE CALDAS KESSLER<sup>2</sup>;

LEOMAR SOARES DA ROSA JÚNIOR<sup>3</sup>

<sup>1</sup>*Universidade Federal de Pelotas – vdmandowski@inf.ufpel.edu.br*

<sup>2</sup>*Universidade Federal de Pelotas – hckessler@inf.ufpel.edu.br*

<sup>3</sup>*Universidade Federal de Pelotas – leomarjr@inf.ufpel.edu.br*

### 1. INTRODUÇÃO

O desempenho de um circuito integrado depende diretamente da qualidade do projeto das portas lógicas utilizadas. O número de transistores em um chip cresce de modo exponencial concomitantemente à sua complexidade (MOORE, 1965), a biblioteca de células torna o projeto factível, visto que os fabricantes disponibilizam um conjunto de células previamente projetadas e caracterizadas eletricamente. No entanto, essa vantagem também torna-se uma restrição, pois limita a capacidade de otimização do circuito à sua biblioteca de células.

A caracterização elétrica é o processo que consiste em medir e analisar os comportamentos elétricos das redes de transistores dos circuitos integrados por meio de simulações elétricas. Existem três métricas fundamentais para buscar otimizar um circuito com base em sua caracterização, sendo elas o atraso de resposta do sistema, o consumo de potência e a área ocupada pelo circuito (WESTE; HARRIS, 2011).

Portas lógicas são blocos fundamentais na eletrônica que realizam operações elementares, tais como negação, disjunção (OR) e conjunção (AND). Essas portas são compostas por redes de transistores projetadas e caracterizadas nas bibliotecas de células para simplificar o desenvolvimento de dispositivos eletrônicos, como smartphones e computadores.

Caso um projetista queira otimizar o seu circuito criando sua própria porta lógica, ele pode optar em usar portas lógicas complexas. As portas lógicas complexas podem executar funções lógicas mais sofisticadas, contudo, essas portas lógicas não se encontram presentes nas bibliotecas de células. O motivo de não existir um fluxo de projeto de portas complexas, é o elevado grau de complexidade de leiaute e o desconhecimento de seu nicho de utilização.

O dimensionamento é responsável pelas características elétricas do transistor, e este, é dinâmico de acordo com a característica do pulso de entrada na porta lógica e também sua carga de saída. Dito isso, em uma biblioteca de células, existem portas lógicas com dimensionamentos variados para garantir que exista uma porta com comportamento elétrico satisfatório para todas as situações, estes dimensionamentos são usualmente denotados pela variável "W".

Para realizar o dimensionamento, existem técnicas de dimensionamento, como por exemplo a técnica baseada no *Logical Effort* (SUTHERLAND; SPROULL; HARRIS, 1999) que será referenciada neste trabalho como 'LE'. Outra técnica presente na literatura, é uma adaptação do LE focada em portas complexas, a qual inclui um fator de multiplicação série(S) e paralelo(P) para dimensionar os transistores juntamente com o LE (BÖHLKE, 2021). Para referência ao longo deste trabalho, denominaremos essa técnica como 'Técnica SP'.

Nesse contexto, o presente trabalho pretende avaliar os métodos já discutidos na literatura (KESSLER et al., 2022) (BÖHLKE, 2021) (SUTHERLAND; SPROULL; HARRIS, 1999) para o dimensionamento de transistores em portas lógicas. Junto a estas técnicas, pretende-se propor uma abordagem metodológica alternativa, focando em modelos assimétricos de dimensionamento, com o objetivo de otimizar as características das portas lógicas complexas em relação às técnicas já existentes.

## 2. METODOLOGIA

Partindo da premissa de que uma abordagem de dimensionamento assimétrico pode apresentar resultados favoráveis em portas complexas, foi conduzida uma simulação elétrica em uma rede complexa de transistores utilizando a tecnologia de 40nm. Para realizar as simulações elétricas, utilizou-se o SPICE, *Simulation Program with Integrated Circuit Emphasis*, que é um programa de simulação de circuitos eletrônicos que permite simular o comportamento de transistores sem a necessidade de fabricá-los. Para o projeto das portas lógicas usadas no SPICE, foi empregada a ferramenta SwitchCraft (CALLEGARO et al., 2010). Essa ferramenta gera, a partir de uma função lógica, o arranjo de transistores de acordo com a topologia selecionada no SPICE.

Com o uso do SPICE, primeiramente criou-se o ambiente de simulação onde o *Design Under Test* (DUT) (Design de teste) foi construído. Para isso, as matrizes de entrada (*Input Array*) foram conectadas a inversores em série nas entradas do circuito (*Fan In*), a fim de proporcionar um com um atraso mais realista. Inversores em paralelo foram aplicados como cargas de saída do circuito (*Fan Out*). Durante as simulações, a quantidade de inversores em paralelo na saída foi ajustada, permitindo que o dimensionamento seja realizado para diferentes valores de cargas de saída.

Com a implementação dos DUTs, incluiu-se as variáveis a serem medidas para comparação das técnicas, que incluem o *Slope* (declive), atraso de propagação e consumo dinâmico de potência. O *Slope* é uma forma de medir o atraso do circuito a partir das inclinações da curva da tensão de saída do DUT. Isto envolve comparar um ponto em 20% da rampa com um ponto em 80% de tensão, tanto para subidas quanto para descidas das curvas. O atraso de propagação é o tempo que a saída do circuito demora para responder ao pulso de entrada, medido através da diferença em que a saída muda seu nível lógico em relação à entrada. O consumo dinâmico é a dissipação de potência que ocorre durante as transições de estados do circuito, calculado multiplicando-se a corrente elétrica pela tensão do circuito durante a mudança de estado.

Com o intuito de validar os experimentos e identificar um possível nicho para as portas complexas e a assimetria de dimensionamento, os resultados obtidos nas simulações foram comparados com as técnicas de dimensionamento LE (SUTHERLAND; SPROULL; HARRIS, 1999) e SP (BÖHLKE, 2021). O LE consiste em uma abordagem para estimar o atraso de propagação de um circuito. Para isso, é necessário aumentar as dimensões dos transistores de uma porta lógica com base na quantidade de transistores em série entre a alimentação e o nó de saída do transistor. Por exemplo, considerando uma porta lógica com dimensionamento W e um caminho em que três transistores estão em série, estes transistores teriam um dimensionamento três vezes maior que W.

Embora a técnica LE seja bastante eficaz para portas lógicas simples, pode não ser tão adequada para portas complexas, conforme (KESSLER et al., 2022). Neste contexto, a técnica SP (BÖHLKE, 2021) teve como objetivo melhorar as características de consumo de potência das portas lógicas complexas, utilizando a técnica LE como base e fazendo algumas modificações de dimensionamento.

As técnicas existentes na literatura dimensionam os transistores de maneira simétrica, aplicando as mesmas regras de dimensionamento a transistores que se encontram em caminhos distintos entre a alimentação e a saída. No entanto, uma abordagem de dimensionamento assimétrico poderia trazer melhores resultados, pois dado que os caminhos críticos determinam o atraso de um circuito, um dimensionamento assimétrico poderia diminuir o W de transistores que não fazem parte do caminho crítico, visando ganhos em potência sem prejudicar o atraso. Essa abordagem assimétrica envolve aplicar o fator de multiplicação diferente do LE ou de outras técnicas de dimensionamento aos caminhos não críticos do circuito.

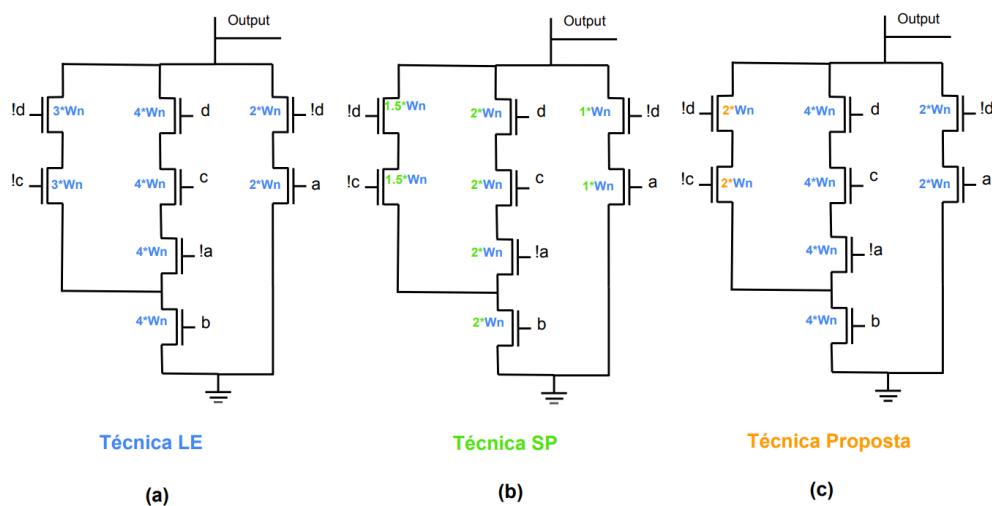

Para os experimentos, foram simuladas 5 portas lógicas, com cargas *Fan Out* 4 (FO4) e *Fan Out* 32 (FO32). A Figura 1 ilustra um arranjo de transistores, no qual implementou-se diferentes técnicas de dimensionamento, utilizando o LE (SUTHERLAND; SPROULL; HARRIS, 1999) na Figura 3.a, a Técnica SP (BÖHLKE, 2021) na Figura 3.b e a Técnica Proposta na Figura 3.c que estabelece uma assimetria em seu dimensionamento, a fim de obter melhores resultados.

Figura 1 – Implementação de técnicas de dimensionamento

Adaptado de: (KESSLER et al., 2022).

### 3. RESULTADOS E DISCUSSÃO

A Tabela 1 apresenta as medidas extraídas das simulações elétricas das 5 portas lógicas, normalizadas em função do LE. Os resultados obtidos foram satisfatórios, uma vez que a técnica proposta demonstrou, no geral, ganhos no atraso de propagação em relação a outras técnicas, para uma carga com 32 inversores (*Fan Out* 32).

Os melhores resultados em termos de consumo de energia foram observados na Técnica SP. Isso se deve ao fato de que essa técnica reduz consideravelmente o tamanho dos transistores, resultando em ganhos de eficiência no consumo de potência, contudo, a técnica proposta demonstrou melhores resultados de consumo de potência, quando comparada ao LE.

Tabela 1 – Resultados de Simulação das Técnicas de Dimensionamento

| Porta Lógica | Métrica  | FO4    |        |          | FO32   |        |          |

|--------------|----------|--------|--------|----------|--------|--------|----------|

|              |          | LE     | SP     | Proposta | LE     | SP     | Proposta |

| Porta 1      | Atraso   | 1,0000 | 1,0156 | 0,9653   | 1,0000 | 1,0055 | 0,9830   |

|              | Slope    | 1,0000 | 1,0070 | 1,0707   | 1,0000 | 1,0031 | 0,9978   |

|              | Potência | 1,0000 | 0,7049 | 0,9540   | 1,0000 | 0,8837 | 0,9818   |

| Porta 2      | Atraso   | 1,0000 | 1,0093 | 1,3205   | 1,0000 | 0,9911 | 0,9761   |

|              | Slope    | 1,0000 | 0,9182 | 0,9662   | 1,0000 | 1,0022 | 0,9987   |

|              | Potência | 1,0000 | 0,7536 | 0,9555   | 1,0000 | 0,9180 | 0,9851   |

| Porta 3      | Atraso   | 1,0000 | 0,9570 | 1,1926   | 1,0000 | 0,9824 | 0,9843   |

|              | Slope    | 1,0000 | 1,0155 | 1,0899   | 1,0000 | 1,0020 | 0,9986   |

|              | Potência | 1,0000 | 0,7127 | 0,9630   | 1,0000 | 0,8949 | 0,9863   |

| Porta 4      | Atraso   | 1,0000 | 0,9999 | 1,3709   | 1,0000 | 0,9898 | 1,0571   |

|              | Slope    | 1,0000 | 0,9668 | 0,9796   | 1,0000 | 0,9880 | 0,9987   |

|              | Potência | 1,0000 | 0,6782 | 0,9752   | 1,0000 | 0,8667 | 0,9895   |

| Porta 5      | Atraso   | 1,0000 | 1,0008 | 0,9561   | 1,0000 | 0,9904 | 1,0452   |

|              | Slope    | 1,0000 | 1,0325 | 1,1769   | 1,0000 | 1,0026 | 1,0108   |

|              | Potência | 1,0000 | 0,7152 | 0,9237   | 1,0000 | 0,8973 | 0,9724   |

#### 4. CONCLUSÕES

Com base nos experimentos realizados, observou-se que uma técnica assimétrica de dimensionamento de transistores em portas complexas pode oferecer resultados promissores, quando comparadas a outras abordagens, principalmente para cargas maiores e com ênfase no atraso de propagação. A técnica ainda se encontra em desenvolvimento e, com base nesses resultados, tem como objetivo buscar alterações para que também obtenha bons resultados de atraso de propagação para cargas pequenas.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

BÖHLKE, M. S. **Adaptação ao Logical Effort: Mantendo a Simplicidade e Reduzindo o Consumo em Portas Complexas**. 2021. Monografia - Curso de graduação em Engenharia de Computação, Universidade Federal de Pelotas.

CALLEGARO, Vinicius et al. **SwitchCraft: a framework for transistor network design**. In: Proceedings of the 23rd symposium on Integrated circuits and system design. 2010. p. 49-53.

MOORE, Gordon. **Moore's law**. Electronics Magazine, v. 38, n. 8, p. 114, 1965.

KESSLER, Henrique et al. **Calibration of Logical Effort Transistor Sizing for On-the-Fly Low-Power Supergate Design**. In: 2022 IEEE 13th Latin America Symposium on Circuits and System (LASCAS). IEEE, 2022. p. 1-4.

WESTE, Neil HE; HARRIS, David Money. Integrated circuit design. **CMOS VLSI Design: A Circuits and Systems Perspective**, 2011.

SUTHERLAND, Ivan; SPROULL, Robert F.; HARRIS, David. **Logical effort: designing fast CMOS circuits**. Morgan Kaufmann, 1999.