## HARDWARE DEDICADO DE ALTO DESEMPENHO PARA A ESTIMAÇÃO DE DISPARIDADE DO PADRÃO 3D-HEVC

MURILO PERLEBERG<sup>1</sup>; VLADIMIR AFONSO<sup>2</sup>;

BRUNO ZATT<sup>1</sup>, MARCELO PORTO<sup>1</sup>

<sup>1</sup>*Universidade Federal de Pelotas – {mrperleberg, zatt, porto}@inf.ufpel.edu.br*

<sup>2</sup>*Instituto Federal Sul Rio-Grandense – vafonso@inf.ufpel.edu.br*

### 1. INTRODUÇÃO

Atualmente, a indústria do entretenimento possui uma grande atenção por conteúdos em três dimensões (3D), os quais visam ampliar a experiência do usuário em diferentes aplicações, com vídeo games ou ainda vídeos 3D. Os vídeos 3D requerem uma série de técnicas de compressão devido a grande quantidade de dados necessários para representar estes vídeos. Assim, o padrão de codificação 3D-HEVC (3D-High Efficiency Video Coding) (ITU-T, 2013) foi lançado em fevereiro de 2015 para suprir a necessidade de comprimir estes vídeos.

O padrão 3D-HEVC herda várias ferramentas de codificação do padrão HEVC (ITU-T, 2013) como a ferramenta ME (Estimação de Movimento), a qual é responsável por reduzir a redundância presente entre quadros vizinhos temporais, isso é, entre quadros que já foram codificados. Contudo, o 3D-HEVC introduz várias ferramentas novas para codificar as características específicas de vídeos 3D, como a possibilidade de representar a cena utilizando diferentes vistas capturadas de diferentes ângulos. Uma dessas ferramentas introduzidas é a DE (Estimação de Disparidade), a qual é responsável por reduzir a redundância de dados presente entre quadros de diferentes vistas, isto é, características da cena que foram capturadas por mais de uma câmera (TECH, 2016).

Ambas as ferramentas ME e DE trabalham com blocos chamados de PU (Unidades de Predição), os quais possui 24 diferentes tamanhos que vão de 4x4 até 64x64 amostras (TECH, 2016). A decisão de qual será o tamanho de bloco a ser utilizado para codificar cada parte do quadro do vídeo é decidido por um processo com alto custo computacional, o qual avalia o custo baseado no equilíbrio entre a taxa de compressão e a qualidade visual. A avaliação de todos os tamanhos possibilita ao padrão 3D-HEVC uma alta eficiência de compressão, porém com um custo computacional extremamente alto, de forma que essas duas ferramentas podem consumir até 98% do tempo total da codificação de um vídeo.

Existem diversos trabalhos propondo soluções para reduzir a complexidade da ME, ou ainda apresentando arquiteturas capazes de aplicar a ME em vídeos em tempo real. Contudo, apenas poucos trabalhos possuem foco nas características da etapa DE. O trabalho (AFONSO, 2018) propõe o algoritmo UDS, sendo o primeiro trabalho da literatura a propor um algoritmo completamente focado a ferramenta DE do padrão 3D-HEVC. O trabalho (PERLEBERG, 2018) apresenta uma solução arquitetura para a DE utilizando o UDS, porém suportando apenas 4 tamanhos de bloco.

Já o trabalho (AFONSO, 2019) propõe um sistema completo contemplando as ferramentas ME e DE utilizando o algoritmo HDS, que é uma extensão do UDS, porém explorando alguns candidatos em posições verticais. Contudo, este último considera a utilização de apenas dois tamanhos de PU. Sendo assim, este trabalho apresenta uma arquitetura de baixo consumo energético com uma alta

taxa de processamento para a etapa DE, adotando um algoritmo focado nas características dessa etapa, enquanto realiza o processamento de todos os tamanhos de PU possíveis.

## 2. METODOLOGIA

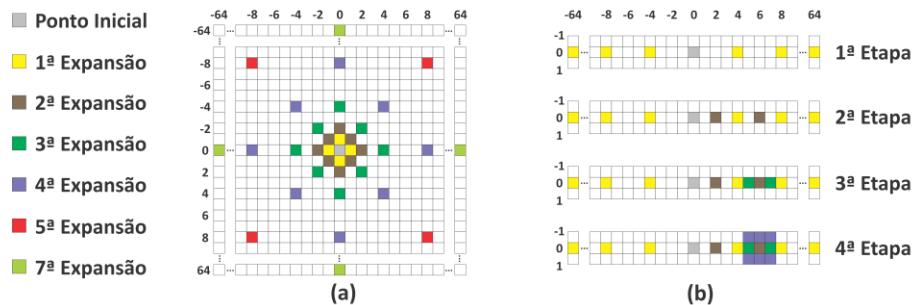

A ferramenta DE é responsável por reduzir a redundância entre vistas, através de um processo altamente custoso. Na DE, diversos blocos pertencentes a uma área de busca são avaliados, em busca do bloco mais similar ao bloco que está sendo codificado. O *software* de referência do padrão 3D-HEVC, o 3D-HTM (3D-HEVC Test Model) (HEVC) adota o algoritmo Test Zone Search como padrão para as ferramentas ME e DE, o qual possui a sua principal estrutura de busca representada na Figura 1-(a). Contudo, o 3D-HEVC foi desenvolvido considerando que as vistas capturadas estão distribuídas horizontalmente. Logo, os blocos candidatos de posições verticais possuem uma baixa probabilidade de serem selecionados como melhor candidato. Sendo assim, algoritmos como o UDS e o HDS se propõem a eliminar ou restringir a avaliação de blocos localizados verticalmente, avaliando principalmente candidatos horizontais.

O HDS foi proposto em (AFONSO, 2019), sendo um algoritmo de 4 etapas, sendo que cada etapa possui um parâmetro de subamostragem, o qual dita quais serão os blocos a serem avaliados. Contudo, AFONSO (2019) possui a deficiência de ter sido avaliado junto com outras alterações no codificador, não tendo sido avaliado sozinho com maiores detalhes. Assim, para este trabalho, utilizamos os parâmetros 4-2 e avaliando os 6 candidatos ao redor do melhor candidato obtido, conforme pode ser visto na Figura 1-(b), que exibe os candidatos avaliados em cada etapa. Este ponto de operação foi avaliado através de experimentos realizados utilizando a ferramenta 3D-HTM (HEVC) na versão 16.2, considerando a configuração de acesso randômico e as condições comuns de teste do padrão 3D-HEVC (MÜLLER, 2014). As avaliações mostraram que este ponto de operação possui um impacto na eficiência de compressão de 0,2363% considerando a métrica BD-Rate, a qual representa o percentual de acréscimo no número de bits do vídeo comprimido para manter uma mesma qualidade na imagem (BJONTEGAARD, 2008).

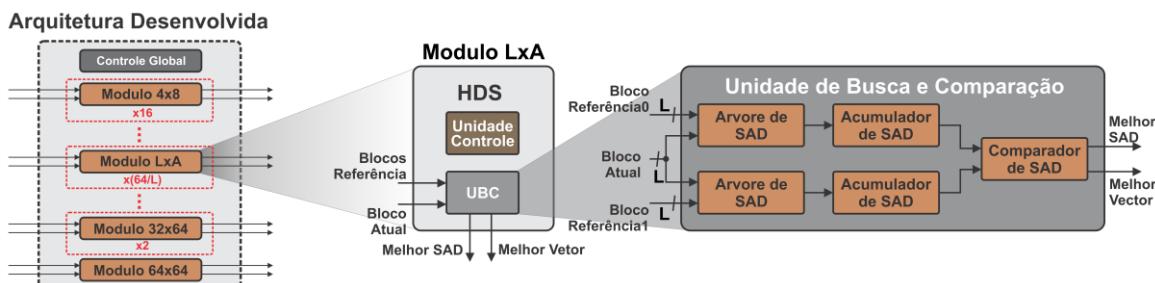

Sendo assim, a arquitetura foi desenvolvida para o ponto de operação avaliado. O diagrama de blocos da arquitetura pode ser visto na Figura 2. Pode ser visto que a arquitetura possui diversos módulos, sendo cada módulo implementa o algoritmo HDS para lidar especificamente com apenas um único tamanho de PU. Todos estes módulos trabalham em paralelo, buscando atingir o processamento de altas resoluções. Também pode ser visto pela Figura 2 que cada módulo possui duas unidades. A primeira delas é a unidade de controle, a qual utiliza o algoritmo HDS para selecionar dois a dois os candidatos a serem avaliados. Já a segunda unidade é a Unidade de Busca e Comparação, a qual processa os dois candidatos escolhidos com o bloco sendo codificado baseado na

Figura 1 – Representação dos algoritmos. (a) Algoritmo TZS. (b) Algoritmo HDS.

Figura 2 – Diagrama de blocos da arquitetura desenvolvida.

métrica SAD (soma das diferenças absolutas), a qual é comumente utilizado nas arquiteturas da literatura por ser uma métrica de baixo esforço computacional. O diagrama de blocos de uma Unidade de Busca e Comparação (UBC) também pode ser visto na Figura 2. Esta unidade processa os 2 blocos selecionados em paralelo, sendo processado uma linha de cada bloco candidato a cada ciclo de clock. Assim, essa unidade possui duas árvores de SAD, dois acumuladores e um comparador de duas entradas.

Cada árvore de SAD é responsável por calcular o valor do SAD entre a linha do candidato que está sendo processada e a respectiva linha do bloco sendo processado. O valor do SAD obtido é então passado para os acumuladores, o qual processa os valores de SAD obtidos, enquanto as árvores de SAD processam o resto das linhas do bloco sendo processado. Assim, quando todas as linhas forem processadas, o Acumulador possuirá o valor do SAD respectivo a cada um dos blocos candidatos. Esse valor é então passado ao comparador de SAD, o qual verifica qual o candidato mais similar ao bloco sendo codificado, sendo o que possuir o menor valor de SAD.

A arquitetura foi dividida por diversos registradores de *pipeline*, visando atingir uma maior taxa de processamento. Os diversos registradores utilizados foram distribuídos de forma que apenas uma ou duas operações aritméticas fosse executada em cada estágio de *pipeline*.

### 3. RESULTADOS E DISCUSSÃO

A arquitetura desenvolvida foi descrita com a linguagem Verilog HDL, e sintetizada para ASIC considerando a biblioteca de células da Nangate de 45nm. Os resultados obtidos podem ser vistos na Tabela 1, juntamente com os resultados de outros trabalhos disponíveis na literatura. Embora um destes trabalhos seja para a etapa ME do padrão HEVC, alguns resultados da arquitetura (como a dissipação de energia e o consumo de área) pode ser comparado, visto que as etapas ME e DE são similares. Contudo, a eficiência de compressão dessas soluções não pode ser comparada visto elas foram avaliadas utilizando diferentes contextos, e também diferentes vídeos.

Conforme pode ser visto pela tabela 1, a arquitetura proposta requer mais recursos do que (FAN, 2018), mesmo processando os mesmos tamanhos de PU.

Tabela 1 – Resultados e comparações com trabalhos relacionados

| Trabalhos Relacionados                              | Fan (2018)        | Perleberg (2018)       | Este Trabalho    |

|-----------------------------------------------------|-------------------|------------------------|------------------|

| Ferramenta                                          | HEVC ME           | 3D-HEVC DE             | 3D-HEVC DE       |

| Tamanhos de PU                                      | Todos os 24       | Quatro                 | Todos os 24      |

| Algoritmo                                           | TZS Modificado    | UDS                    | HDS              |

| Aumento no BD-rate                                  | –                 | 0,554%                 | 0,236%           |

| Área Total (gates)                                  | 489,4k            | 395,6k                 | 3243k            |

| 1080p@60fps                                         | Frequência        | 500MHz                 | 82.31            |

| 1 Vista                                             | Potência/Tensão   | 128.5mW/Não Disponível | 105.8 MHz        |

| Processamento de vídeos 3D de resolução 2160p@60fps | Não (0.25 vistas) | 9.99mW/0.95V           | 90.72mW/0.95V    |

|                                                     |                   | Sim (3.4 vistas)       | Sim (3.4 vistas) |

Contudo, os resultados da síntese mostram que a arquitetura proposta dissipava uma potência 29% menor do que (FAN, 2018), além de ser capaz de processar sequências 4320x2160p com mais de três vistas a 60qps em tempo real, enquanto que (FAN, 2018) não é capaz de processar uma vista de mesma resolução em tempo real. Quando comparado com (PERLEBERG, 2018), foi obtido a mesma taxa de processamento, porém com um maior consumo de recursos computacionais e um maior consumo de potência, o que é esperado visto que a arquitetura proposta suporta o processamento de todos os tamanhos de PU, obtendo assim um menor impacto na taxa de compressão, o que é importante em aplicações que requerem uma maior qualidade visual.

Por fim, alterando o algoritmo TZS pelo algoritmo HDS na etapa DE, além de resultar em melhores resultados da arquitetura, também resulta em reduções no tamanho da memória, visto que apenas um pequeno refinamento vertical é realizado. Com isso, a memória necessária para os blocos de referência é de apenas 192x66 amostras, enquanto que o algoritmo TZS requeria 192x192 amostras de referência. Essa redução afeta tanto os recursos computacionais necessários, mas também o consumo de potência destes recursos.

#### 4. CONCLUSÕES

Este trabalho apresentou uma arquitetura de alto desempenho para a ferramenta Estimação de Disparidade do padrão 3D-HEVC, utilizando o algoritmo HDS. Uma análise foi realizada para investigar o impacto desse algoritmo na eficiência de compressão. Os resultados de síntese mostraram que a arquitetura proposta consegue atingir uma maior taxa de processamento do que os demais trabalhos encontrados na literatura para a mesma ferramenta, sendo a única capaz de processar vídeos 3D com resolução 3840x2160p a 60qps.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

- AFONSO, V. et al. Hardware-Friendly Unidirectional Disparity-Search Algorithm for 3D-HEVC. **International Symposium on Circuits and Systems**, Italy, 2018.

- AFONSO, V. et al. Energy-Aware Motion and Disparity Estimation System for 3D-HEVC with Run-Time Adaptive Memory Hierarchy, **IEEE Transactions on Circuits and Systems for Video Technology**, vol. 29, n. 6, 2019.

- BJONTEGAARD, G. Improvements of the BD-PSNR model, VCEG-AI11, 2008.

- FAN, Y. et al. A hardware-oriented IME algorithm for HEVC and its hardware implementation. **IEEE Transactions on Circuits and Systems for Video Technology**, vol. 28, n. 8, 2018.

- HEVC. HEVC Reference Software. Disponível em: <<http://hevc.hhi.fraunhofer.de>>.

- ITU-T. H.265 High efficiency video coding. Recommendation ITU-T, 2013.

- MÜLLER, K. et al. Common Test Conditions of 3DV Core Experiments, JCT3V-G1100, San Jose, 2014.

- PERLEBERG, M. et al. A Power-Efficient and High-Throughput Hardware Design for 3D-HEVC Disparity Estimation. **Symposium on Integrated Circuits and Systems**, Bento Gonçalves, 2018.

- TECH, G. et al. Overview of the Multiview and 3D Extensions of High Efficiency Video Coding, **Transactions on Circuits and Systems for Video Technology**, vol. 26, n. 1, 2016.