## BIBLIOTECA DE PORTAS LÓGICAS NML UTILIZANDO O ESQUEMA DE CLOCK BANCS

GABRIEL SOARES; MAICON CARDOSO; FELIPE MARQUES; LEOMAR ROSA

*Universidade Federal de Pelotas – {gsdsoares, mscardoso, felipem, leomarjr}@inf.ufpel.edu.br*

### 1. INTRODUÇÃO E MOTIVAÇÃO

A tecnologia CMOS, amplamente utilizada no desenvolvimento de processadores, está próxima de seu limite físico. Além disso, a mesma ainda enfrenta problemas relacionados ao alto consumo energético(CAVIN; LUGLI; ZHIRNOV, 2012). Devido às dimensões do transistor atual – que atinge a escala de nanômetros –, uma grande parte da energia dos circuitos é perdida com correntes de fuga, fazendo com que *chips* CMOS dissipem mais potência.

Esses fatores fizeram com que houvesse a necessidade de se propor novas tecnologias para atuar em conjunto e, em determinados casos, substituir o CMOS. Dentre as tecnologias propostas, uma que vem tendo grande destaque é a *nanomagnetic logic* (NML) (POROD; BERNSTEIN; CSABA; HU; NAHAS; NIEMER; ORLOV, 2014), especialmente devido a sua ultra-baixa dissipação de energia. Apesar de não conseguir alcançar frequências tão altas como o *quantum-dot cellular automata* (QCA) (LENT; SNIDER, 2014) – outro potencial candidato a suceder o CMOS –, o NML é possível de ser implementado em temperatura ambiente, diferentemente do QCA, o qual necessita de temperaturas próximas ao zero absoluto para a realização dos cômputos.

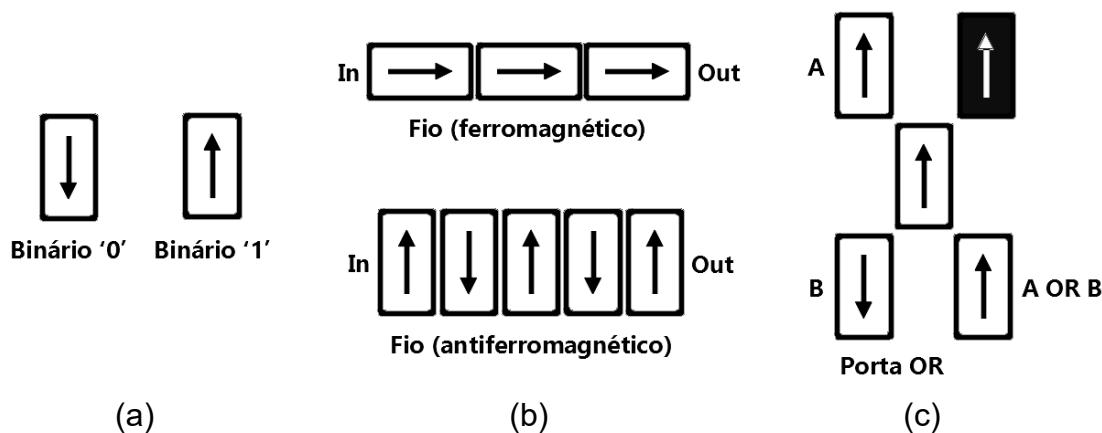

Figura 1. Nanomagnetic Logic.(a) Estados binários; (b) Acoplamentos ferromagnético (à esq.) e antiferromagnético (à dir.); (c) Porta OR em NML.

No NML, os valores binários ‘0’ e ‘1’ são associados à orientação da polarização dos nanomagnets (Figura 1.a), tal que, utilizando-se da interação e posicionamento entre os mesmos, torna-se possível realizar operações lógicas

como em portas lógicas convencionais. Nesse cenário, existem dois tipos de acoplamentos magnéticos na tecnologia: o ferromagnético e o antiferromagnético (Figura 1.b). Para manter os valores corretos durante a polarização e evitar uma mudança de sentido na propagação do sinal, faz-se necessário a aplicação de um *clock* externo. Além disso, tal sinal de *clock* permite a sincronização do circuito.

A fim de propiciar uma maior praticidade no projeto em NML, mostrou-se eficiente o emprego de um esquema de *clock*, o qual potencializa o desenvolvimento de algoritmos para posicionamento e roteamento automático de células.

Nesse cenário, visando facilitar o desenvolvimento de sistemas digitais complexos em NML, este trabalho propõe uma biblioteca de células no esquema *Bidirectional Alternating Nanomagnetic Clocking Scheme* (BANCS) (FORMIGONI; NACIF; NETO, 2018), apresentando características como latência, área de leiaute e número de magnetos para cada instância do banco de portas lógicas projetado.

## 2. METODOLOGIA

Visando demonstrar a escalabilidade da tecnologia NML, foram selecionados circuitos simples a serem implementados que podem ser usados para compor sistemas digitais mais complexos. Além desses, ainda escolheram-se circuitos que aparecem com frequência em trabalhos da área. Portanto, as portas implementadas foram: AOI22, C17, *latch-D*, MUX2-1, XOR2, XOR5, *parity checker*, *parity generator*, *latch-SR*, *half adder* e *full adder*.

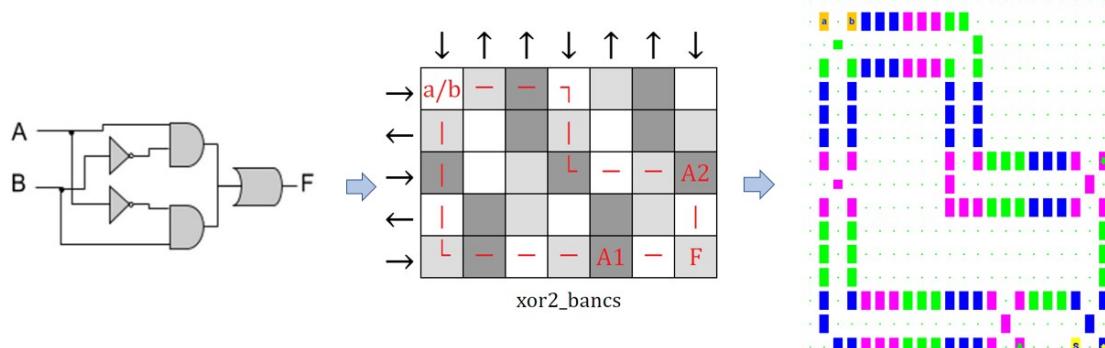

Utilizando o diagrama lógico de cada circuito escolhido e o esquema de *clock* BANCS, criou-se um leiaute de alto nível (ou seja, nível de projeto) para garantir a sincronia das portas lógicas.

Figura 2. Fluxo de desenvolvimento de uma porta XOR2: diagrama lógico, projeto e leiaute do circuito.

A partir do leiaute anterior e com o auxílio da ferramenta NMLSim (SOARES; RAHMEIER; LIMA, 2018), criaram-se os circuitos NML para simulação e validação. Começando pelos circuitos simples, os quais foram utilizados como componentes para os maiores, até os circuitos complexos e que não utilizam portas pré-projetadas. Com as soluções devidamente projetadas e validadas,

realizou-se a extração dos dados para a caracterização dos elementos da biblioteca.

### 3. RESULTADOS E DISCUSSÃO

Os circuitos obtidos através da metodologia proposta anteriormente apresentaram os resultados esperados, validando os layouts gerados. Os dados obtidos tornam mais fácil a utilização das células como componentes, pois com a informação de latência (*delay*) e área, a sincronização entre diferentes células em um circuito maior torna-se trivial.

Além disso, através do desenvolvimento realizado, comprovou-se a escalabilidade dos circuitos através do BANCS, dado que utilizou-se a porta *XOR2* como componente para o *half adder*, e esse último como componente para o *full adder*. Pode-se concluir que a geração de circuitos como somadores e multiplicadores torna-se facilitada a partir do uso da biblioteca projetada.

Foram extraídos de cada circuito os seguintes dados: área, altura e largura da porta lógica, total de magnetos e latência em ciclos de *clock* (*delay*). Abaixo é apresentada uma tabela com alguns dos dados obtidos.

| Circuito              | Área* | Altura* | Largura* | Magnetos | Delay** |

|-----------------------|-------|---------|----------|----------|---------|

| AOI/22                | 99    | 11      | 9        | 30       | 2       |

| C17                   | 1332  | 36      | 37       | 318      | 8       |

| <i>Latch-D</i>        | 560   | 16      | 7        | 152      | 7       |

| <i>MUX2-1</i>         | 182   | 14      | 13       | 57       | 3       |

| <i>XOR2</i>           | 315   | 15      | 21       | 107      | 4       |

| <i>XOR5</i>           | 2142  | 51      | 42       | 742      | 21      |

| <i>Par. checker</i>   | 1156  | 34      | 34       | 361      | 9       |

| <i>Par. generator</i> | 936   | 36      | 26       | 288      | 10      |

| <i>Latch-SR</i>       | 147   | 7       | 21       | 32       | 3       |

| <i>Half adder</i>     | 600   | 20      | 30       | 152      | 4       |

| <i>Full adder</i>     | 2394  | 42      | 57       | 418      | 10      |

Tabela 1. Dados obtidos. \*Medida em magnetos. \*\*Medido em ciclos.

### 4. CONCLUSÕES E TRABALHOS FUTUROS

A biblioteca de células já se mostrou útil ao longo da implementação desses circuitos ao facilitar o desenvolvimento de portas complexas como o *half adder* e o

*full adder*, os quais utilizaram-se de outros componentes pertencentes ao banco. Isso mostra a importância da existência de um repositório de circuitos já implementados e validados, contendo dados que auxiliam a sua utilização. Porém, cabe salientar que o número de circuitos implementados ainda é pequeno.

Para trabalhos futuros, planeja-se ampliar a biblioteca, aumentando o número de circuitos e a sua variedade, além de reimplementar os elementos da biblioteca em outros esquemas de *clocks* a fim de aumentar a diversidade e permitir que o utilizador tenha a possibilidade de escolher o esquema que possui as células mais adequadas para o seu projeto.

Serão desenvolvidos também dois algoritmos para o apoio ao projeto em NML: para a extração automática dos dados e para a verificação da função lógica implementada pelo circuito. O primeiro algoritmo visa a redução de erros humanos que possam ocorrer ao extraír dados, aumentando a eficiência nessa etapa. O segundo, verificador functional, tem como objetivo deixar mais simples a identificação da função lógica implementada. Nele, o usuário entraria com os sinais de saída gerados pela simulação do NMLSim e com a função lógica que espera que esteja implementada, e o algoritmo retornaria a confirmação de que o comportamento esperado fora obtido.

## 5. REFERÊNCIAS BIBLIOGRÁFICAS

Cavin, Ralph & Lugli, Paolo & Zhirnov, V.V.. (2012). **Science and Engineering Beyond Moore's Law.** Proceedings of the IEEE. 100. 1720-1749. 10.1109/JPROC.2012.2190155.

Formigoni, Ruan; Vilela Neto, Omar; Miranda Nacif, José. (2018). **BANCS: Bidirectional Alternating Nanomagnetic Clocking Scheme.** 1-6. 10.1109/SBCCI.2018.8533251.

Lent C.S., Snider G.L. (2014) **The Development of Quantum-Dot Cellular Automata.** In: Anderson N., Bhanja S. (eds) Field-Coupled Nanocomputing. Lecture Notes in Computer Science, vol 8280. Springer, Berlin, Heidelberg

Porod, Wolfgang; Bernstein, Gary; Csaba, György; Hu, Sharon ; Nahas, Joseph; Niemier, Michael; Orlov, Alexei. (2014). **Nanomagnet Logic (NML).** 10.1007/978-3-662-43722-3\_2.

Soares; T.R.B.S.; Nizer Rahmeier; J.G.; de Lima, V.C. et al. J Comput Electron (2018) 17: 1370. **NMLSim: a Nanomagnetic Logic (NML) circuit designer and simulation tool.**