## UM ESTUDO SOBRE A SATD – SOMA DAS DIFERENÇAS ABSOLUTAS TRANSFORMADAS UTILIZANDO A TRANSFORMADA DE HADAMARD 2x2

LUIZ GUILHERME MARTINHO SAMPAIO ITO<sup>1</sup>; MARCELO DA COSTA LOPES<sup>2</sup>;

BIANCA SANTOS DA CUNHA DA SILVEIRA<sup>3</sup>

<sup>1</sup>Universidade Federal de Pelotas – llguilherme@hotmail.com

<sup>2</sup>Universidade Federal de Pelotas – tecmarcelolopes@gmail.com

<sup>3</sup>Universidade Federal de Pelotas – biancascsilveira@gmail.com

### 1. INTRODUÇÃO

Vídeos demandam uma grande taxa de bits para serem renderizados, porém essa taxa pode ser reduzida com técnicas de compressão de vídeo (AGOSTINI, 2007).

A compressão de vídeo, por sua vez, consiste em diminuir o tamanho de um vídeo (com ou sem perda), através de técnica que remove das imagens as informações que já foram projetadas (SILVA, 2007).

Considerando que os atuais meios de recepção e transmissão de imagem demandam cada vez mais de dados, como a TV digital (SILVEIRA, 2016), a compressão de vídeo é de grande importância. Para solucionar este problema, foram desenvolvidos padrões de compressão de vídeo ao longo dos anos, sendo os principais: MPEG-1 (ISO/IEC, 1993), MPEG-2 (ITU-T, 1994), MPEG-4(ISO/IEC, 1999) e padrões mais novos como o (PEREIRA, 2014) H.264/AVC (*Advanced Video Coding*) (ITU-T; 1, 2011) e o HEVC (*High Efficiency Video Coding*) (ITU-T; ISO/IEC,2013).

O objetivo do presente estudo é analisar a técnica H.264/AVC de compressão de vídeo utilizando da métrica SATD. Para tanto se utiliza revisão bibliográfica dos textos citados nas referências.

### 2. METODOLOGIA

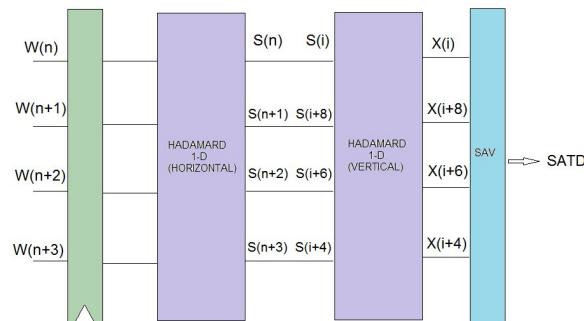

Explora-se a possibilidade da soma de vários operandos simultaneamente, utilizando os circuitos compressores com o menor caminho crítico possível como forma de acelerar os cálculos da SATD (SEIDEL, 2014). A arquitetura desenvolvida, *Hadamard Transform 2x2 2-D* (duas dimensões), foi dividida em dois estágios de 1-D, chamados de Hadamard horizontal e Hadamard vertical. As três arquiteturas seguem o modelo mostrado na Figura 1.

Figura 1 – Modelo da Arquitetura de Hardware da SATD

As transformadas horizontal e vertical recebem 4 amostras de entrada e entregam a saída em um ciclo de *clock*<sup>1</sup>. Os registradores de entrada (em verde na Figura 1) armazenam as amostras de entrada para mantê-las estáveis. As amostras de saída da HT vertical são acumuladas pelo módulo da soma dos valores absolutos (SAV – *Sum of Absolute Values*). O resultado final da SATD acumulado é armazenado em um registrador de saída. A Figura 2 mostra o circuito interno da Hadamard 2x2 1-D.

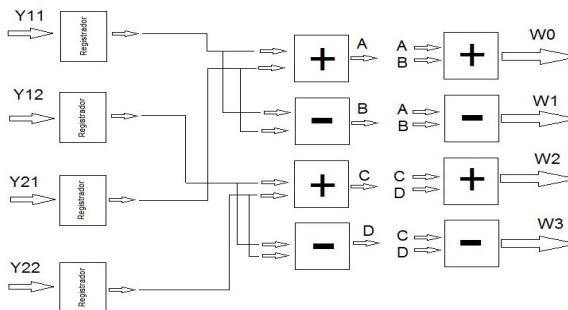

Figura 2 – Bloco do Circuito Interno da Hadamard 2x2 1-D

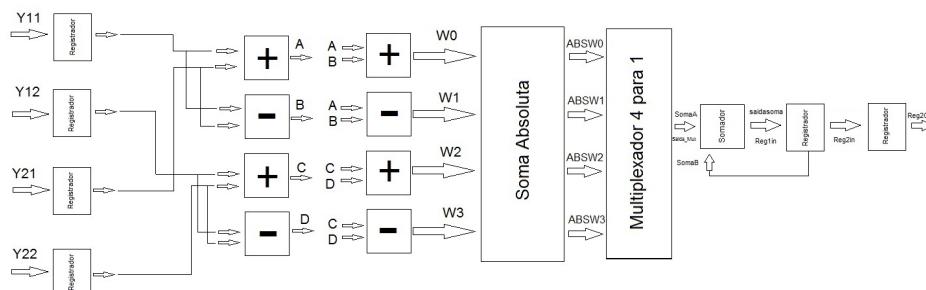

A imagem acima apresenta o circuito interno do módulo SAV original aplicado somadores compressores, enquanto a Figura 3 apresenta este módulo com o somador compressor 4:2.

O circuito interno dos blocos das transformadas Hadamard horizontal e vertical são idênticos mudando somente os valores das entradas e saídas de cada um. O módulo SAV é composto por um conjunto de 4 registradores que armazenam as amostras entregues pela Hadamard vertical, bem como por 4 operadores absolutos e uma árvore de somadores que acumula os valores.

Figura 3 – Circuito Interno do Módulo SAV com Compressor 4:2

Na arquitetura sequencial a Hadamard horizontal recebe 4 amostras de entrada,  $W(n)$  até  $W(n+3)$ . A cada ciclo de *clock* uma linha de amostras do bloco 2x2 é entregue como entrada para a primeira transformada 1-D (horizontal). O bloco inteiro 2x2 é processado em 4 ciclos de *clock* pela Hadamard horizontal.

Os dois estágios 1-D da Hadamard são conectados por um conjunto de quatro registradores sequencial/paralelo e um multiplexador. Eles são responsáveis por ler as quatro saídas da Hadamard horizontal (uma linha do bloco de amostra 2x2) e entregar estes resultados, coluna por coluna, para a Hadamard vertical. Isto é feito porque a Hadamard vertical é aplicada na matriz transposta. Os registradores sequenciais (em cinza na Figura 1) armazenam as quatro saídas da Hadamard horizontal a cada ciclo de *clock*. Após 4 ciclos de

<sup>1</sup> Do inglês, é um sinal usado para coordenar as ações de dois ou mais circuitos eletrônicos.

clock, todas as amostras nos registradores sequenciais são então armazenadas nos registradores paralelos (em verde na Figura 2) e entregues para o multiplexador. Estes multiplexadores são os responsáveis por selecionar os resultados armazenados nos registradores paralelos e entregar coluna por coluna para a Hadamard vertical.

### 3. RESULTADOS E DISCUSSÃO

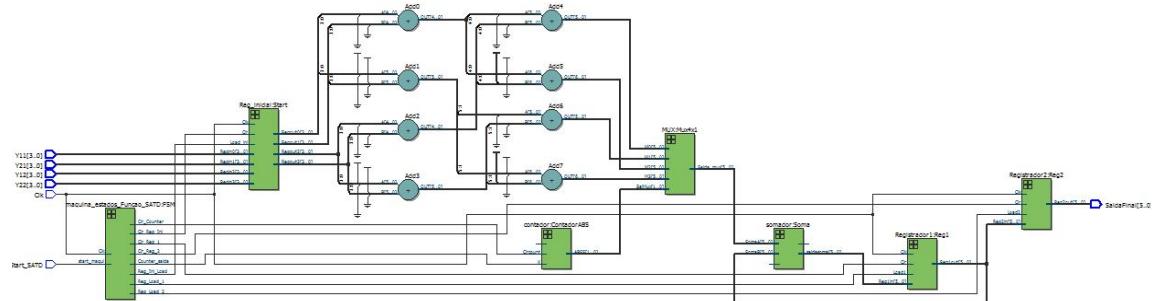

A Figura 4 mostra o  $RTL^2$  da SATD utilizando a Transformada de Hadamard, composto pelos blocos operativos, máquina de estados e a árvore de somadores.

Primeiramente as entradas  $Y_{11}$ ,  $Y_{21}$ ,  $Y_{12}$  e  $Y_{22}$ , são armazenadas em registradores e, em seguida, é feita a diferença de tais entradas. Então, é realizada uma etapa de primeira transformada-1D FHT das diferenças e os resultados são armazenados em um *buffer*<sup>3</sup>.

Os resultados parciais passam então por uma segunda etapa de transformada-1D FHT em seguida, fazendo o absoluto dos valores obtidos da segunda transformada-1D. Os valores absolutos são somados em um esquema de árvore de somas e acumuladores.

Ao final, os valores são inseridos na entrada do multiplexador4x1 e selecionados pelo contador de 2 bits para a entrada do somador que, por sua vez, inicia um *loop*<sup>4</sup> de somas sucessivas com o registrador 2.

O final das somas sucessivas são valores multiplexados e somados para a saída final da SATD.

Figura 4 – RTL da Arquitetura Sequencial com o Bloco de Controle

## 4. CONCLUSÕES

Este trabalho apresentou um estudo sobre a arquitetura SATD dedicada para a compressão de vídeo do padrão HEVC, com enfase na técnica para o aumento de desempenho e redução de potência.

<sup>2</sup> Do inglês Register Transfer Level, é utilizada na representação do circuito de baixo nível do qual derivam-se as conexões do hardware.

<sup>3</sup> Do inglês, é uma região de memória física utilizada para armazenar temporariamente os dados enquanto eles estão sendo movidos de um lugar para outro.

<sup>4</sup> Do inglês, é um conjunto de instruções que um programa de computador percorre e repete um significativo número de vezes até que sejam alcançadas as condições desejadas.

O trabalho demonstrou uma técnica de paralelismo do cálculo da Transformadas Hadamard 2x2, utilizando de somadores compressores do próprio simulador *Quartus II* para o cálculo da SATD de forma que o circuito tenha um reaproveitamento de bits, consequência disso, uma redução de potência.

## 5. REFERÊNCIAS BIBLIOGRÁFICAS

AGOSTINI, L. V. **Desenvolvimento de Arquiteturas de Alto Desempenho dedicadas à compressão de vídeo segundo o Padrão H.264/AVC.** 2007. 172f. Tese (Doutorado) - Programa de Pós-Graduação em Computação, Universidade Federal do Rio Grande do Sul.

PEREIRA, F. At all. *H. 264 8x8 inverse transform architecture optimization. Proceeding of the 24th Edition od the Great Lakes Symposium on VLSI*, USA, 2014.

SEIDEL, I. **Análise do impacto de pel decimation na codificação de vídeos de Alta resolução.** 2014. Dissertação (Mestrado) – Programa de Pós-Graduação em Ciências da Computação, Universidade Federal de Santa Catarina.

SILVA, A. M. C. **Um Estudo Sobre o Padrão H.264/avc de Compressão de Vídeo.** 2007. 44f. Dissertação (Qualificação Mestrado) - Programa de Pós-Graduação em Informática, Universidade Católica de Pelotas.

SILVEIRA, B.S.C. **Exploração Arquitetural nas Métricas de Similaridade para Codificadores de Vídeo do Padrão HEVC.** 2016. 69f. Dissertação (Mestrado em Engenharia Eletrônica e Computação.) – Programa Mestrado em Engenharia Eletrônica e Computação, Universidade Católica de Pelotas.