## AJUSTE DO DIMENSIONAMENTO DE PORTAS LÓGICAS REALIZADO PELO LOGICAL EFFORT

HENRIQUE KESSLER; MAICON CARDOSO; RENATO DE SOUZA;

VITOR LIMA; LEOMAR DA ROSA JR.

*Universidade Federal de Pelotas – {hckessler, mscardoso, rsdsouza, vgdlima,

leomarjr}@inf.ufpel.edu.br}*

### 1. INTRODUÇÃO

Devido à complexidade dos *chips*, para que o projeto seja realizado de forma eficiente, faz-se necessário o uso de diversas ferramentas dedicadas às diferentes etapas do fluxo de síntese digital. De forma resumida, a especificação parte do nível de transferência de registradores (RTL), onde linguagens de descrição de *hardware* são utilizadas. Após esse primeiro estágio, realiza-se o mapeamento tecnológico, onde os componentes do sistema são descritos como redes de transistores, os quais devem ser dimensionados, posicionados e conectados de forma a respeitar as restrições do projeto.

Acerca do dimensionamento de portas lógicas (*sizing*), esse estágio da síntese digital consiste em determinar o tamanho da largura do *gate* de seus transistores, caracterizando-o em relação ao atraso, consumo de energia e área do circuito. Um dos principais objetivos do *sizing* é, justamente, minimizar algum destes aspectos a fim de se adequar aos requisitos descritos nas especificações do projeto. O primeiro algoritmo a tentar solucionar o problema de dimensionamento de transistores foi TILOS (FISHBURN; DUNLOP, 1985), onde buscava-se reduzir o atraso dos caminhos críticos de forma heurística até satisfazer as restrições do projeto. No entanto, o método de *sizing* mais conhecido é o Logical Effort (SUTHERLAND, 1999). Através dele, define-se o esforço lógico de uma função Booleana de acordo com a topologia adotada, tal que o circuito mais otimizado é aquele cujo esforço lógico é menor. Quando aplicado ao dimensionamento, computa-se a proporção entre os transistores PMOS e NMOS de forma que a placa *pull-up* e *pull-down* do inverter mínimo possua o mesmo atraso.

Assim, o método proposto busca aprimorar o dimensionamento realizado a partir do Logical Effort. Conforme descrito a seguir. Isso é feito a partir da análise de simulações *spice* e modificações realizadas através de iterações sucessivas nos dispositivos que formam a porta lógica.

### 2. METODOLOGIA

Conforme ilustrado na Figura 1, o primeiro passo da metodologia proposta consiste em calibrar o Logical Effort para a tecnologia alvo (nesse caso, utilizamos 350 nm). Para definir a inclinação do sinal de entrada (*slope*), utiliza-se o atraso de propagação de dois inversores mínimos em série em relação a uma onda quadrada. A capacidade conectada à saída da porta é estabelecida pela métrica *fanout-of-4 inverter delay* (FO4) (HARRIS, 1997), onde o valor é a capacidade de um nó conectado a quatro inversores mínimos em paralelo. Buscando definir a proporção entre os transistores PMOS e NMOS, faz-se necessário igualar os tempos de transição entre o placa *pull-up* e *pull-down* de um inverter com os dados encontrados anteriormente. Este ajuste é feito redimensionando o transistor PMOS, onde a proporção entre os tamanhos é o parâmetro do método.

Figura 1 – Fluxo da metodologia proposta.

Na sequência, utiliza-se o Logical Effort com seus parâmetros calibrados para dimensionar a porta lógica. Calculam-se os arcos de transição da função e verifica-se, através de simulação *spice*, os valores dos atrasos das transições baixo-alto (TD\_LH) e alto-baixo (TD\_HL) para cada um dos arcos. Em posse destes dados, é necessário definir qual é o transistor envolvido no arco responsável pelo atraso crítico de cada plano. Esse que possuir o maior atraso deve ser redimensionado de maneira a reduzir a diferença.

Após definido o atraso crítico de cada plano, fixa-se o que possuir o menor valor como o objetivo do dimensionamento do outro. O ajuste é realizado através de modificações sucessivas na largura do *gate* e de simulações *spice*. A condição de parada é atendida quando este transistor não definir o atraso crítico do seu plano. A dimensão desejada é aquela cuja diferença entre os planos é menor. Ademais, verifica-se se a redução do tamanho dos transistores que possuem tempo menor que o crítico não impacta de forma significativa no atraso, de forma a reduzir a área total e a capacidade dos nós conectados.

### 3. RESULTADOS E DISCUSSÃO

Para avaliar a qualidade do método proposto foi feito um estudo de caso na função Booleana  $f$  descrita em (1), onde esta foi passada como entrada para a ferramenta SwitchCraft (CALLEGARO, 2010) gerando sua rede de transistores. Esta rede foi dimensionada utilizando o método Logical Effort calibrado, onde o *slope* encontrado foi de 41,734 ps, o FO4 possui a capacidade de 16,921 fF e a proporção entre os transistores PMOS e NMOS foi de 2,197  $\mu\text{m}$ .

$$f = !(a \cdot (b + c)) \quad (1)$$

Verificou-se através de simulações *spice* que o dimensionamento obtido via Logical Effort gera uma diferença considerável entre o atraso crítico dos planos *pull-up* e *pull-down*, permitindo a aplicação da metodologia proposta. A Tabela 1 apresenta os valores encontrados por este dimensionamento, onde PD\_LH e PD\_HL são os atrasos de propagação baixo-alto e alto-baixo, respectivamente, e TD\_LH e TD\_HL são os atrasos de transição baixo-alto e alto-baixo, respectivamente.

Tabela 1 – Atrasos da rede dimensionada através do Logical Effort.

| Arco | PD_LH (ps)    | PD_HL (ps)    | TD_LH (ps)     | TD_HL (ps)     |

|------|---------------|---------------|----------------|----------------|

| a01  | 86,308        | 68,801        | 156,353        | 113,715        |

| a10  | <b>97,165</b> | 88,791        | <b>209,807</b> | 146,696        |

| a11  | 94,510        | 57,007        | 167,529        | 93,482         |

| 1b0  | 85,747        | <b>89,066</b> | 149,055        | <b>146,709</b> |

| 10c  | 77,556        | 76,611        | 149,012        | 113,697        |

Analisando os atrasos, verificou-se que o transistor controlado pela variável  $a$  é responsável pelo atraso crítico do plano *pull-up*. Aplicando a metodologia proposta, foi simulado esse transistor com largura entre 1,500  $\mu\text{m}$  e 3,500  $\mu\text{m}$  e passos de 0,100  $\mu\text{m}$ . Também é possível verificar que o transistor ligado à variável  $c$  participa somente de atrasos abaixo do crítico. Com isso, foram explorados os dimensionamentos entre 1,000  $\mu\text{m}$  e 2,500  $\mu\text{m}$  considerando a mesma precisão.

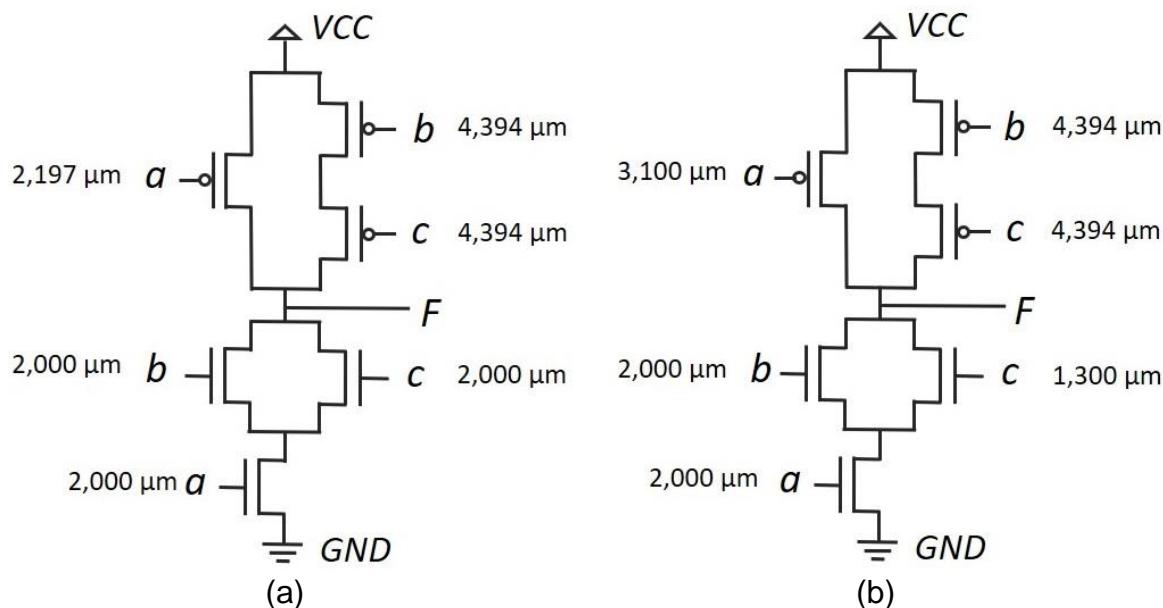

A diferença entre o dimensionamento do Logical Effort e da metodologia proposta no transistor ligado à  $a$  é de 2,197  $\mu\text{m}$  para 3,100  $\mu\text{m}$ , enquanto no transistor controlado por  $c$  é de 2,000  $\mu\text{m}$  para 1,300  $\mu\text{m}$ . A Figura 2 ilustra ambos os dimensionamentos, onde a (a) representa a rede dimensionada pelo Logical Effort e (b), pela metodologia proposta. Os atrasos da nova rede de transistores seguem conforme a Tabela 2.

Figura 2 – Redes de transistores dimensionadas pelos dois métodos.

Tabela 2 – Atrasos da rede dimensionada pela metodologia proposta.

| <i>Arco</i> | <i>PD_LH (ps)</i> | <i>PD_HL (ps)</i> | <i>TD_LH (ps)</i> | <i>TD_HL (ps)</i> |

|-------------|-------------------|-------------------|-------------------|-------------------|

| a01         | 61,232            | 92,089            | 106,588           | 146,883           |

| a10         | 69,978            | 91,431            | 147,396           | 147,117           |

| a11         | 67,073            | 60,530            | 114,357           | 96,178            |

| 1b0         | <b>86,041</b>     | 89,388            | <b>149,711</b>    | <b>147,126</b>    |

| 10c         | 75,354            | <b>102,031</b>    | 149,689           | 146,882           |

As modificações geradas pela metodologia proposta resultaram na redução do pior *delay* de transição em 28,67% e a diferença dos atrasos entre os planos em 95,90%. Estes valores foram adquiridos ao custo de um aumento de 5,00% no maior atraso de propagação da célula.

## 4. CONCLUSÕES

Conclui-se que é possível refinar o dimensionamento feito pelo método Logical Effort quando utilizado para o dimensionamento de redes diferentes de um inversor mínimo. Analisando o estudo de caso realizado, é possível ver a viabilidade do método, pois verifica-se a existência da possibilidade de reduzir a diferença entre os atrasos críticos de transição dos planos. A metodologia proposta apresentou bons resultados sem impactar no funcionamento lógico do circuito.

Como trabalhos futuros, pretende-se fazer o mesmo experimento para um conjunto maior de células a fim de verificar a sua real viabilidade, criando uma biblioteca com os ajustes necessários para reduzir estes atrasos.

## 5. REFERÊNCIAS BIBLIOGRÁFICAS

FISHBURN, J. P.; DUNLOP, A. E. **TILOS: a posynomial programming approach to transistor sizing**. International Conference on Computer Aided Design. 1985. p. 326-328.

SUTHERLAND, I., et. al. “**Logical Effort: designing fast cmos circuits**”. San Francisco, CA, USA: Morgan Kaufmann Publishers Inc., 1999.

HARRIS, D., et. al. **The Fanout-of-4 Inverter Delay Metric**. 1997. Acessado em 24 ago. 2018. Disponível em: [https://www.researchgate.net/publication/237124562\\_The\\_Fanout-of-4\\_Inverter\\_Delay\\_Metric](https://www.researchgate.net/publication/237124562_The_Fanout-of-4_Inverter_Delay_Metric)

CALLEGARO, V., et. al. “**Switchcraft - A framework for transistor network design**.” SBCCI'10 - Proceedings of the 23rd Symposium on Integrated Circuits and Systems Design. 49-53.