## ARQUITETURA DE HARDWARE DA 1D-DCT 4X4 APROXIMADA UTILIZANDO O SOMADOR IMPRECISO LOA

MATEUS TERRIBELE LEME; LUCIANO BRAATZ;

LUCIANO AGOSTINI; MARCELO PORTO

Universidade Federal de Pelotas – {mtleme; la.braatz; agostini; porto} @inf.ufpel.edu.br

### 1. INTRODUÇÃO

É presente nos dias de hoje uma ascensão de dispositivos móveis e serviços de *streaming* que processam vídeos. Dados relacionados a vídeos serão os maiores responsáveis por todo tráfego da Internet até 2020, atingindo cerca de 82% (CISCO, 2018). Transmitir vídeos sem nenhum processo de compressão é uma estratégia proibida. Desta forma se tornam propício o uso de técnicas para comprimir estes vídeos, que exploram a redução da informação a ser transmitida sem uma perda significativa na qualidade. O *High-Efficiency Video Coding* (HEVC) é atualmente o estado-da-arte dos codificadores de vídeo, atingindo cerca de 50% da capacidade de compressão que seu antecessor o H.264, mantendo a mesma qualidade visual (SULLIVAN, 2012).

O padrão HEVC dispõe de etapas com grande complexidade computacional, com isso o desenvolvimento de arquiteturas de *hardware* dedicadas é necessário para o processamento destas etapas em dispositivos com restrições energéticas. O foco deste trabalho está na etapa de codificação, onde são aplicados dois tipos de transformadas e suas respectivas inversas, a transformada discreta do cosseno (*DCT*) e a transformada discreta do seno (*DST*). Através desta etapa as amostras processadas são transformadas do domínio espacial para o domínio da frequência, que concentra a informação nas baixas frequências, o que reduz a entropia dos dados e facilita a compressão.

A operação de transformação da *DCT* utilizada no *HEVC* é a *DCT-2D* definida em (1), onde  $N$  e  $M$  são o número de pontos da *DCT*, é a entrada para a posição da matriz de entrada e é o coeficiente de saída pertencente a matriz de saída. Uma abordagem utilizada para simplificar a *DCT-2D* consiste na propriedade da separabilidade (GHANBARI, 2003). A separabilidade compõe-se na aplicação de duas 1D-*DCT* sucessivamente para obter a *DCT-2D*, dessa maneira diminuindo o número de operações de somas e multiplicações na transformada. Em virtude do elevado número de operações nesta etapa de codificação, viabiliza-se a exploração de novos *hardwares* para otimizar o desempenho da operação de transformação no *HEVC*. Uma possível vertente de exploração são os hardwares desenvolvidos sobre arquiteturas baseadas em computação aproximada.

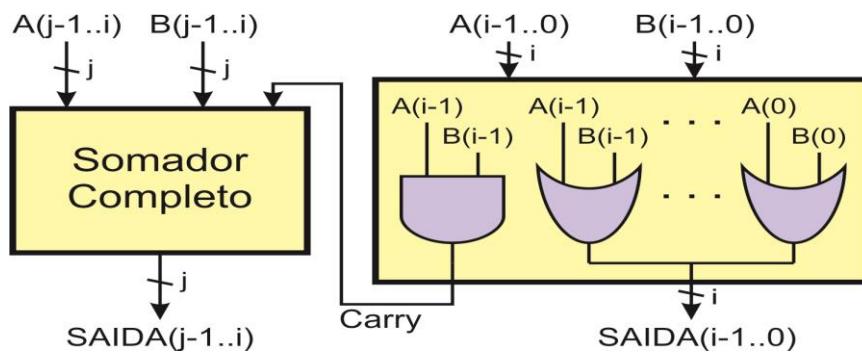

Devido às restrições de energia dos dispositivos moveis a eficiência energética te torna um conceito significante. Contudo, as aplicações de multimídia demandam um alto consumo energético e uma das principais aplicações são os codificadores de vídeo. Então o uso de técnicas para alcançar essa eficiência energéticas são de extrema importância. Uma delas que se baseia no conceito de aplicações tolerantes erros é o uso de operadores aritméticos imprecisos. Codificadores de vídeo por serem uma das maiores aplicações multimídia e por ser suscetíveis a erros, podem se beneficiar em relação a eficiência energética através do uso de operadores imprecisos. Ilustrado na Figura 1 está o circuito do *Lower part Or Adder* (*LOA*) incorporado nos blocos imprecisos propostos por MAHDIANI

$$F(u, v) = \sqrt{\frac{2}{N}} \sqrt{\frac{2}{M}} \sum_{i=0}^{N-1} \sum_{j=0}^{M-1} A_i A_j \cos\left[\frac{\pi u}{2N}(2i+1)\right] \cos\left[\frac{\pi v}{2M}(2j+1)\right] f(i, j) \quad (1)$$

Figura 1- Estrutura do LOA

(2010), sua função é computável é, sendo  $A$  e  $B$  dois números de entrada com largura de bit de tamanho  $j$ . A parcela precisa tem  $j$ . Ambas as larguras dos números são separadas em duas partes de tamanho  $i$  e  $j$ , sendo a soma das partes igual à largura do número. Desta forma é possível tratar a soma em duas etapas: precisa e imprecisa. Para computar a parte precisa é realizada a soma utilizando a arquitetura de um somador completo nos bits mais significativos de  $j-1$  até  $i$ . E a parte imprecisa é computada aplicando a função lógica OU nos bits menos significativos de  $i-1$  até 0, assim gerando o restante dos bits e completando a operação de soma. O bit carry de entrada do somador completo é gerado por uma função lógica E nos bits mais significativos da parte imprecisa.

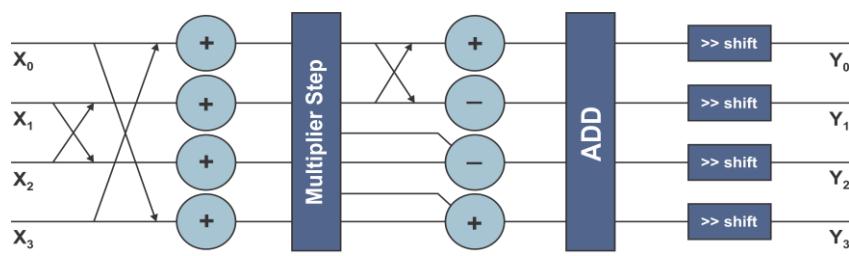

A arquitetura de *hardware* da 1D-DCT 4x4 apresentado na Figura 2 implementa o cálculo do *butterfly*, multiplicação pelos coeficientes da transformada, ajuste dos produtos, soma de um offset para ajuste da largura de bit e por final um deslocamento para a direita. Ao todo são executadas dez somas e duas subtrações para fazer o cálculo da 1D-DCT, no entanto o número total de estrutura de somadores na 2D-DCT é de vinte e quatro. Este trabalho implementa uma arquitetura aproximada de *hardware* utilizando o operador impreciso LOA. Os ganhos em eficiência energética desta proposta de hardware atingiram 42% de redução de potência dissipada com um aumento inexpressivo de 1,18% na eficiência de codificação de vídeo.

## 2. METODOLOGIA

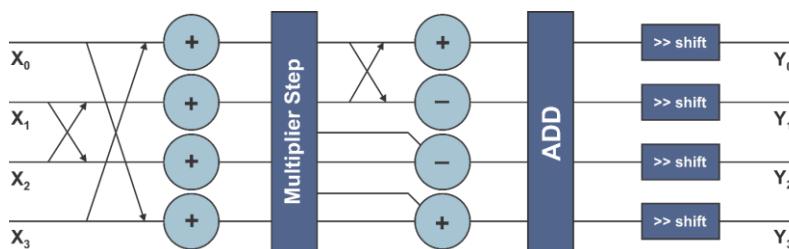

Para realização deste trabalho a seguinte metodologia foi adotada. Primeiramente, foi projetada a proposta da arquitetura aproximada da 1D-DCT 4x4 apresentada na Figura 3. As modificações consistem na remoção do offset e substituição todos os operadores de soma e subtração pelo LOA. Posteriormente verificação no impacto em eficiência de codificação, e por fim, descrição das arquiteturas em VHDL para gerar os valores referentes a eficiência energética. A arquitetura foi descrita em C++ utilizando a biblioteca *Bitset* e foi aplicada ao software de referência *HEVC Test Model HM*, na versão 16.7. Se faz necessário esta etapa para fazer a avaliação do impacto em eficiência de codificação. Neste caso o fator modificador na eficiência de codificação é a imprecisão.

O BD-Rate é a unidade utilizada para medir a eficiência de codificação, é baseado na relação entre qualidade (PSNR) e taxa de bits (*bitrate*) entre duas

Figura 2- Design da 1D-DCT 4x4

Figura 3- Design proposto da 1D-DCT 4x4

amostras original e modificada, onde um resultado negativo indica que foi possível usar uma taxa de bits menor para representar uma mesma qualidade de imagem, e em caso positivo indica que foi necessário uma taxa de bits maior para representar uma mesma qualidade de imagem. Foi realizada a exploração para cinco níveis de imprecisão diferentes apresentados na Tabela 1. É possível notar níveis diferentes de imprecisão entre a primeira 1D-DCT processada e a segundo, isto é possível devido a largura de bits da segunda ser 178% maior que a primeira, assim permitindo uma exploração maior da imprecisão nesta etapa. A Tabela 2 mostra os resultados de eficiência de codificação, para gerar estes resultados foram utilizados três vídeos para cada resolução explorada, de acordo com as recomendações comuns de teste (CTC).

TABELA 1- NÍVEIS DE IMPRECISÃO

| Nível      | IMP1 | IMP2 | IMP3 | IMP4 | IMP5 |

|------------|------|------|------|------|------|

| 1st 1D-DCT | 1    | 3    | 5    | 7    | 9    |

| 2nd 1D-DCT | 3    | 5    | 7    | 9    | 11   |

Nos resultados podemos identificar um aumento no impacto da eficiência de codificação com o aumento do nível de imprecisão. Contudo o impacto foi maior nos vídeos de resolução *Full HD* devido este grupo utilizar mais blocos 4x4 em sua estrutura de particionamento. No entanto os resultados de BD-Rate são insignificantes para um real impacto visual, e mostraram que a DCT utilizada no padrão HEVC é suscetível a erros, desta forma, o uso de operadores imprecisos pode ser utilizado a fim de se obter ganhos de eficiência energética.

### 3. RESULTADOS E DISCUSSÃO

Utilizando *VHDL* seis versões da 1D-DCT 4x4 foram descritas, a original e os cinco níveis diferentes de imprecisão. As seis arquiteturas foram sintetizadas em *ASIC* utilizando a biblioteca de células padrões *Nangate 45nm*. Os resultados apresentados na Tabela 3 mostram um aumento na redução de área e potência dissipada com o aumento do nível de imprecisão. Isto se dá pela diminuição de portas lógicas nas operações de soma, a quebra da cadeia de carry pelo operador

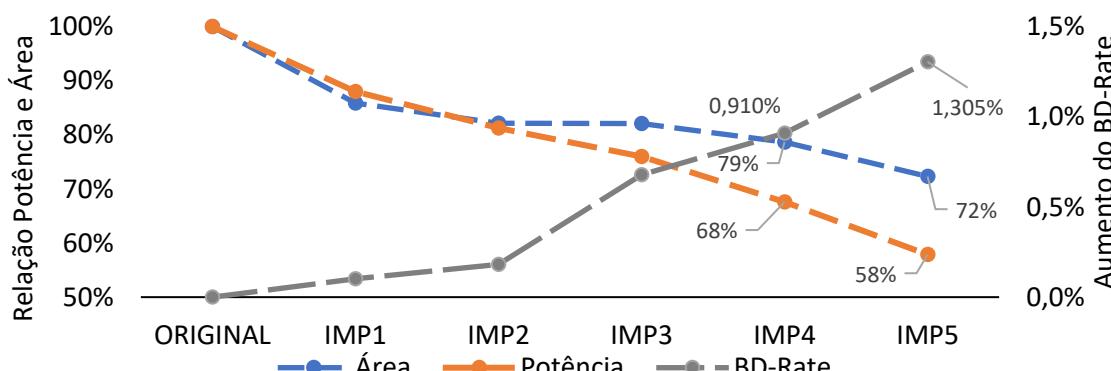

Figura 4 – Relação entre BD-Rate e Eficiência energética

TABELA 2- RESULTADOS DE EFICIÊNCIA DE CODIFICAÇÃO

| Resolução   | BD-rate (%) |       |        |       |       |

|-------------|-------------|-------|--------|-------|-------|

|             | IMP1        | IMP2  | IMP3   | IMP4  | IMP5  |

| Média 1080p | -0,007      | 0,21  | 1,319  | 1,672 | 1,970 |

| Média 4k    | 0,045       | 0,075 | -0,054 | 0,099 | 0,406 |

| Média Total | 0,019       | 0,143 | 0,633  | 0,886 | 1,188 |

LOA, proporcionou um aumento na frequência de operação da arquitetura proposta. No maior nível IMP5 comparada com a versão original sem imprecisão nota-se uma redução de 42% na potência dissipada e 28% de redução de área. A Figura 4 mostra a relação inversamente proporcional entre os resultados de eficiência energética com o impacto na eficiência de codificação, quanto maior a redução de potência dissipada e área maior é o impacto na eficiência de codificação.

TABELA 3- RESULTADOS DA 1D-DCT 4x4 APROXIMADA

| Parâmetros               | ORG   | Variação (%) |      |      |      |      |

|--------------------------|-------|--------------|------|------|------|------|

|                          |       | IMP1         | IMP2 | IMP3 | IMP4 | IMP5 |

| Área ( $\mu\text{m}^2$ ) | 2626  | -14          | -18  | -18  | -21  | -28  |

| Frequência (MHz)         | 467.5 | +7           | +16  | +24  | +25  | +20  |

| Power (mW)               | 1.873 | -12          | -19  | -24  | -32  | -42  |

#### 4. CONCLUSÕES

Usando uma sequência de simulações para mensurar o impacto na eficiência de codificação que resultaram em valores insignificantes no impacto visual, foi possível avaliar a viabilidade da utilização de operadores imprecisos na transformada discreta dos cossenos usada no padrão HEVC. Os resultados de hardware se mostraram promissores em relação a ganhos em eficiência energética, atingindo uma redução de 42% na potência dissipada com um impacto de 1,18% na eficiência de codificação. Como trabalhos futuros pretende-se explorar o uso de somadores imprecisos em todos os tamanhos de blocos onde é aplicada a 1D-DCT no padrão HEVC.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

Cisco, “Cisco Visual Networking Index: Forecast and Methodology 2016-2021” 2018. Online]. Disponível em: <https://www.cisco.com/c/en/us/solutions/collateral/service-provider/visual-networking-index-vni/complete-white-paper-c11-481360.html>.

G. J.Sullivan, J. R. Ohm, W. J. Hanand T. Wiegand. 2012. **Overview of the High efficiency Video Coding (HEVC) Standard**. IEEE Transactions on Circuits and Systems for Video Technology (TCSVT) 22, 12 (2012), 1649 – 1668.

GHANBARI, M. Standard Codecs: Image Compression to Advanced Video Coding. United Kingdom. **The Institution of Electrical Engineers**, 2003.

H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas. Bio-Inspired Imprecise Computational Blocks for Efficient VLSI Implementation of Soft-Computing Applications. **IEEE Transaction On Circuits And Systems—I: Regular Papers**, v. 57, n. 4, 2010.

JCT-VC Editors, **Recommendation ITU-T H.265 -High Efficiency Video Coding (ITU-T Rec.H.265)**, abril 2013. online. Disponível em: <http://handle.itu.int/11.1002/1000/11885>.