## INVESTIGAÇÃO DA TÉCNICA DE DESSINCRONIZAÇÃO EM CIRCUITOS INTEGRADOS: ESTUDO DE CASO COM A ARQUITETURA MIPS PIPELINE

LUCAS REGO DA ROCHA<sup>1</sup>; NICHOLAS DUTRA LIHTNOV<sup>2</sup>; RAFAEL IANKOWSKI SOARES<sup>3</sup>

<sup>1</sup>*Universidade Federal de Pelotas – lrdrocha@inf.ufpel.edu.br*

<sup>2</sup>*Universidade Federal de Pelotas – ndlihtnov@inf.ufpel.edu.br*

<sup>3</sup>*Universidade Federal de Pelotas – rafael.soares@inf.ufpel.edu.br*

### 1. INTRODUÇÃO

A tecnologia *Complementary Metal Oxide Semiconductor* (CMOS), é largamente utilizada na fabricação de bens de consumo tais como smartphones. A evolução da tecnologia CMOS tem permitido um aumento na produção de circuitos integrados mais complexos e com um poder de processamento maior.

A tecnologia CMOS impulsiona o projeto de System on Chip (SoCs), ou seja circuitos integrados compostos por diversos módulos em uma única pastilha de silício. Segundo Pontes (PONTES, 2008), o desenvolvimento de SoCs é quase totalmente baseado no pressuposto da discretização de tempo, onde o processamento e comunicação entre módulos é controlado por um sinal global denominado de relógio.

Este pressuposto também é conhecido como paradigma síncrono de projetos de circuitos digitais, sendo amplamente utilizado pela indústria de dispositivos eletrônicos, segundo Madsen (MADSEN, 2011). Com a redução da tecnologia CMOS a dimensões submicrônicas, o uso do sinal global de relógio para a sincronização das operações em um SoC passa por sérios desafios de projeto. Desafios tais como: o consumo de energia por parte do sinal global de relógio e a distribuição do sinal global de relógio no circuito.

Há diversas alternativas ao paradigma síncrono, uma delas é a técnica da dessincronização. A dessincronização é uma técnica de conversão automática de circuitos síncronos em circuitos sem sinal global de relógio.

O processador MIPS é uma arquitetura Reduced Instruction Set Computer (RISC), sendo utilizado na academia pela organização e simplicidade como exemplar didático. O processador caracteriza-se por possuir um tamanho de palavra e capacidade de endereçamento de 32 bits. Cada endereço de memória armazena um byte de informação.

O processador MIPS apresenta três diferentes versões que se diferem com relação a execução temporal de suas instruções: Monociclo, Multiciclo, Pipeline.

A versão Pipeline do MIPS divide o caminho de dados em 5 partes chamadas de estágios. Cada estágio é encarregado de funções específicas. Dessa forma é possível a concorrência de passos dentro do caminho de dados.

Os objetivos desse trabalho são investigar a técnica da dessincronização aplicada ao processador de propósito geral MIPS pipeline, utilizando um ambiente de desenvolvimento do fluxo *Field Programmable Gate Array*(FPGA) e a linguagem de descrição de hardware *VHSIC Hardware Description Language*(VHDL). Comparar critérios como área, potência dissipada, energia consumida, desempenho na arquitetura dessincronizada em relação ao arquitetura síncrona, utilizando o ambiente de desenvolvimento escolhido do fluxo FPGA.

### 2. METODOLOGIA

Neste trabalho foi utilizado o ambiente de desenvolvimento ISE Xilinx 14.7 para a implementação, verificação e extração de estimativas de características como área, dissipação de potência das arquiteturas. A validação do processador se deu através de testbench. Como estudo de caso proposto foi realizado um conjunto de instruções que realizam a ordenação de dados afim de compreender o comportamento de processamento de uma aplicação real.

## 2.1 A TÉCNICA DA DESSINCRONIZAÇÃO

A técnica da dessincronização é descrita por Cortadella (CORTADELLA et al., 2006), em três passos:

- 1) Conversão de flip-flops síncronos em latches tipo mestre/escravo. Desacoplamento dos sinais de relógio para os latches mestre/escravo.

- 2) Geração de um sinal de fim de computação obtido por um circuito detector de completude. Este sinal deve ser gerado com base no caminho no caminho crítico do circuito combinacional correspondente a computação, devendo ter um atraso superior a este caminho crítico.

- 3) Implementação de controladores para os relógios locais.

## 2.2 EXECUÇÃO DA DESSINCRONIZAÇÃO

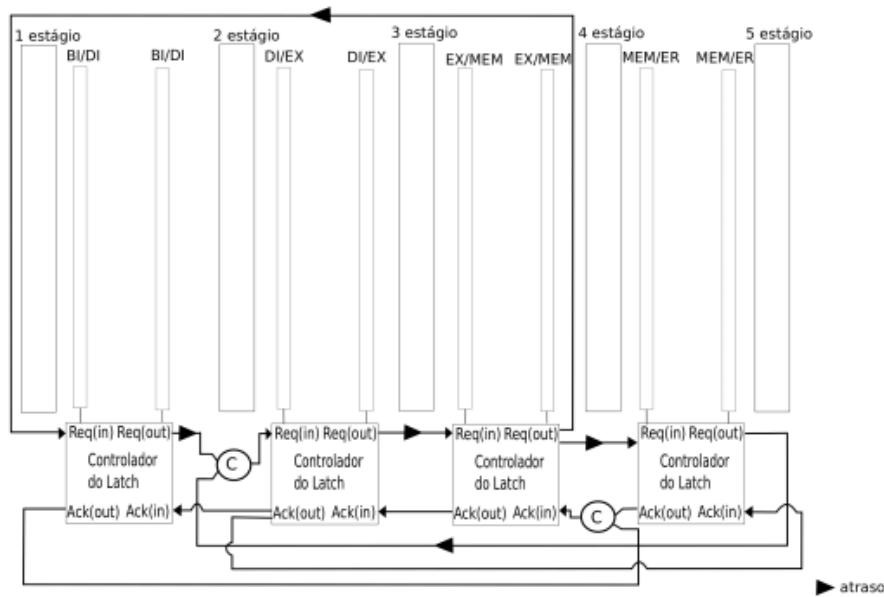

Como explicado pelo autor Madsen (MADSEN, 2011), dentro de circuitos assíncronos o sistema de distribuição de relógio é substituído por um conjunto de sinais *handshake*. Este conjunto de sinais possui a mesma finalidade de sincronização do sinal global de relógio: sinalizar novas entradas no circuito, e possibilita o salvamento de informações finalizadas.

O controlador de *latch*, possui como função principal o acionamento do *latch*, sendo composto por quatro portas de comunicação que realizam a lógica *handshake*. Por combinar simplicidade e um bom desempenho foi utilizado neste trabalho o controlador inspirado na configuração de (CORTADELLA et al., 2006), sendo na tecnologia semidesacoplada e formado por dois submódulos de controlador. A descrição em VHDL do controlador se deu através de máquinas de estado representando a lógica dos submódulos, cada submódulo possuindo duas máquinas de estado.

Atrasos combinados são utilizados como detectores de completude das partes combinacionais, são essenciais para a técnica da dessincronização, sendo representados pelo interior dos estágios na arquitetura MIPS Pipeline. Os atrasos foram descritos na linguagem VHDL através de diretivas não prototipáveis.

O método de medição deste atraso foi realizado através da retirada individual de cada estágio do caminho de dados. Ele é sintetizado no ambiente de desenvolvimento em meio a registradores na entrada e saída, o ambiente de desenvolvimento então retorna uma estimativa de atraso.

A construção do caminho de dados da arquitetura dessincronizada, ocorreu através da medição dos atrasos combinados, observando a dinâmica de envio e recepção de informações de cada estágio. Sendo detectado que algum estágio envia ou recebe informações de mais de um estágio é utilizado a estrutura *Fork*, *Join*. A estrutura lida com múltiplos envios(*Fork*) ou pedidos(*Join*) de informações.

Após a retirada do sinal de relógio global, é inserido um controlador para cada estágio. *Fork* e *Joins* são inseridos. Os controladores inseridos são conectados. Atrasos combinados são inseridos nos fios de *request in* dos controladores. Os sinais de relógio locais são gerados através da redireção do sinais de *acknowledge out* dos controladores. O caminho de dados do processador

dessincronizado é apresentado na Figura 1, possuindo um *Fork* no estágio 4 e um *Join* no estágio 2.

### 3. RESULTADOS E DISCUSSÃO

Dentro das configurações do ambiente de desenvolvimento foram escolhidas as opções: Família Spartan-3A DSP, dispositivo XC3SD1800A. Os resultados se dividem em área, desempenho, dissipação potência e consumo de energia. Todos os resultados são observados na Tabela 1.

Tabela 1: Críterios de comparação arquiteturas MIPS Pipeline.

| Critérios                       | Arquitetura<br>Dessincronizada | Arquitetura<br>Síncrona |

|---------------------------------|--------------------------------|-------------------------|

| Número de Slices Ocupadas       | 2125                           | 2018                    |

| Número total de LUTs 4 entradas | 2762                           | 2855                    |

| Potência dissipada(milliWatt)   | 167                            | 124                     |

| Energia Consumida(W x ms)       | 4,55                           | 2,65                    |

| Atraso médio (nanosegundos)     | 17,79                          | 14                      |

Figura 1: A arquitetura MIPS Pipeline dessincronizada.

No critério de área a arquitetura dessincronizada obteve um *overhead* em relação a síncrona de 5,04% em *Slices* ocupados, que são justificados pela adição de lógica *handshake*. A arquitetura dessincronizada obteve uma redução de área de 3,25% número total de LUTs de 4 entradas se comparado com a arquitetura síncrona no critério é especulado que isto ocorra em razão de otimizações realizadas pela ferramenta de síntese.

No critério de desempenho foi escolhido o atraso médio, sendo obtido através de regra de três entre: tempos de término de computação das arquiteturas executando o estudo de caso e período da arquitetura síncrona. É obtido então o atraso médio da arquitetura dessincronizada. A arquitetura dessincronizada é 27%

vezes mais lenta que a síncrona. O resultado de desempenho é justificado pela necessidade de sinais *handshake* percorrerem caminho crítico(controladores, *Fork* e *Join*) para realizar a sincronização. É especulado que os *Forks* e *Joins* podem causar um gargalo devido a necessidade de esperar a conformidade de sinais de dois diferentes estágios para a sinalização. O método de coleta de atrasos gerando estimativas pessimistas, não se baseando na síntese física do hardware.

O critério da potência dissipada na arquitetura dessincronizada aumentou em cerca de 34,68% em relação a arquitetura síncrona. O aumento potência dissipada da arquitetura dessincronizada em relação a síncrona é justificada pelo aumento expressivo do *hardware*. O critério da energia consumida na arquitetura dessincronizada obteve um aumento expressivo de cerca de 71,70% em comparação com a arquitetura síncrona, isto se justifica pela estimativa ser dependente da potência dissipada e do tempo de processamento, sendo ambos tiveram aumento, haverá um impacto na energia consumida.

#### 4. CONCLUSÕES

O trabalho executado foi a descrição na linguagem VHDL da arquitetura dessincronizada MIPS Pipeline, utilizando o ambiente de desenvolvimento no fluxo FPGA. O resultado do trabalho é uma arquitetura simulável a nível comportamental mas não prototipável devido ao uso de diretivas e dificuldades técnicas com relação aos atrasos combinacionais. O produto principal é uma discussão sobre a viabilidade e dificuldades da aplicação da técnica da dessincronização dentro do fluxo FPGA. A principal contribuição é a obtenção da arquitetura sem o uso do sinal global de relógio que é simulável em nível comportamental.

Como trabalhos futuros a principal expansão deste trabalho é obtenção de atrasos combinados combinacionais e estimativas baseadas na síntese física do hardware. Alternativamente o uso de outras formas de inserção de atrasos, o método proposto por Garcia (GARCIA et al., 2014) onde é utilizado um protocolo Bundled data duas fases, onde é possível a síntese em qualquer dispositivo lógico programável com performance aumentando em 21% na média e com um overhead de 27% dentro das LUTs.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

- CORTADELLA, J.; KONDRATYEV, A.; LAVAGNO, L.; SOTIRIOU, C. P. Desynchronization: Synthesis of Asynchronous Circuits From Synchronous Specifications. *IEEE Trans. on CAD of Integrated Circuits and Systems*, [S.I.], v.25, n.10, p.1904–1921, 2006.

- GARCIA, K.; OLIVEIRA, D. L.; CURTINHAS, T.; D'AMORE, R. Synthesis of locally-clocked asynchronous systems with bundled-data implementation on FPGAs. In: IX SOUTHERN CONFERENCE ON PROGRAMMABLE LOGIC(SPL), 2014., 2014. *Anais*. . . [S.I.: s.n.], 2014. p.1–6.

- MADSEN, R. **Desynchronization of digital circuits**. 2011. 143f. Dissertação (Mestrado em Ciência da Computação) - DTU Informatics, Technical University of Denmark.

- PONTES, J. J. H. **PROJETO E PROTOTIPAÇÃO DE INTERFACES E REDES INTRACHIP NÃO-SÍCRONAS EM FPGAS**. 2008. 115p. Dissertação (Mestre em Ciência da Computação) — PONTIFÍCIA UNIVERSIDADE CATÓLICA DO RIO GRANDE DO SUL, Porto Alegre, 2008.