## COMPARAÇÕES ENTRE SOMADORES HÍBRIDOS DE DOIS OPERANDOS

MARIANE SAMPAIO BARROS<sup>1</sup>; CLÁUDIO MACHADO DINIZ<sup>2</sup>; EDUARDO ANTONIO CÉSAR DA COSTA<sup>3</sup>; RAFAEL DOS SANTOS FERREIRA<sup>4</sup>; MATEUS BECK FONSECA<sup>5</sup>

<sup>1</sup>Universidade Federal de Pelotas. Centro de Engenharias. Curso de bacharelado em Engenharia Eletrônica – sampaio.barros@hotmail.com

<sup>2</sup>Universidade Católica de Pelotas – claudio.diniz@ucpel.edu.br

<sup>3</sup>Universidade Católica de Pelotas – eduardo.costa@ucpel.edu.br

<sup>4</sup>Universidade Católica de Pelotas – rsferreira82@gmail.com

<sup>5</sup>Universidade Federal de Pelotas. Centro de Engenharias. – beckfonseca@gmail.com

### 1. INTRODUÇÃO

O consumo de potência vem sendo apontado como um dos principais parâmetros em projetos de circuitos integrados. Aspectos de baixa dissipação de potência exigem a pesquisa de novas arquiteturas confiáveis que possam ser testadas e fabricadas e que levem em consideração as necessidades de sistemas eletrônicos portáteis de funções diversas. (Ferreira, 2016)

Uma classe de algoritmos que tem merecido especial atenção, com aspectos de baixa potência, são os algoritmos de DSP (do Inglês: Processamento Digital de Sinais) e a codificação de vídeo. De fato, este interesse tem sido intensificado desde a proliferação de equipamentos eletrônicos portáteis de alto desempenho operados por baterias, tais como telefones celulares, tablets, equipamentos biomédicos, e outros. (Costa, 2002)

A implementação de operadores aritméticos operando diretamente em código Híbrido (Costa, 2002), mostra que é possível a implementação destes operadores com características de baixa potência.

Baseando-se nisso, este trabalho visa compreender a arquitetura e codificação de somadores híbridos, a fim de aplicá-los em somadores aritméticos eficientes.

### 2. METODOLOGIA

Foram estudadas duas topologias diferentes de somadores híbridos (versões A e B), descritas na linguagem de descrição de hardware VHDL. A fim de realizar a simulação e a codificação dos dados, foi escolhida a ferramenta ModelSim, devida a sua disponibilidade de versão estudante. Ainda pretende-se realizar a síntese ASIC (do inglês: Circuitos Integrados de Aplicação Específica).

A descrição de hardware deu-se da seguinte maneira: cada estrutura foi descrita conforme sua arquitetura lógica, em diferentes larguras de bits (2, 4, 8,..., n bits). Após a descrição, cada código foi compilado e, não ocorrendo nenhum erro, foi realizada a simulação, mostrando seus devidos resultados de soma.

### 3. RESULTADOS E DISCUSSÃO

Até o momento, conta-se com códigos VHDL de até 16 bits, com o intuito de obter maior facilidade em encontrar erros ou de otimizar os códigos. As figuras a seguir mostram umas das arquiteturas descritas (versão A), um dos códigos descritos e seu respectivo resultado.

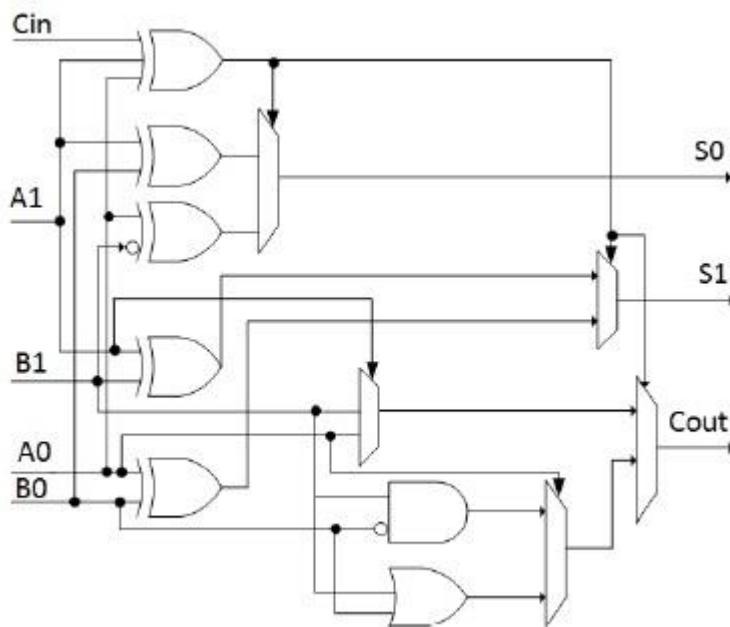

Figura 1- Somador Híbrido: versão A

```

1  -- Version A Hybrid Adder: 4-bits

2  -- Developer: Mariane Sampaio Barros, academica do curso

3  |----- de Bacharelado em Engenharia Eletronica

4  -- Pelotas, agosto de 2017

5

6  library ieee;

7  use ieee.std_logic_1164.all;

8  use ieee.std_logic_misc.all;

9  use ieee.numeric_std.all;

10 use ieee.std_logic_signed.all;

11

12

13 entity hyb_adder_a_4_bits is

14  port (

15    a      : in std_logic_vector(3 downto 0);

16    b      : in std_logic_vector(3 downto 0);

17    cin   : in std_logic;

18    cout  : out std_logic;

19    s     : out std_logic_vector(3 downto 0)

20  );

21 end hyb_adder_a_4_bits;

22

23 -- descrição comportamental do sistema

24 architecture rtl of hyb_adder_a_4_bits is

25

26 component hyb_adder_a  -- somador hibrido de 2 bits

27  port (

28    a0      : in std_logic;

29    a1      : in std_logic;

30    b0      : in std_logic;

31    b1      : in std_logic;

32    cin    : in std_logic;

33    cout   : out std_logic;

34    s0     : out std_logic;

35    s1     : out std_logic

36  );

37 end component;

```

Figura 2- Código Descrito para 4 bits

```

38

39     signal cout0_cin1 : std_logic;    -- interconexão do cout do adder0 com o cin do adder1

40

41 begin

42

43     adder0: hyb_adder_a

44     port map ( a0  => a(0), --

45                 |al  => a(1),

46                 b0  => b(0),

47                 bl  => b(1),

48                 cin  => cin,

49                 cout => cout0_cin1,

50                 s0  => s(0),

51                 sl  => s(1)

52             );

53

54     adder1: hyb_adder_a

55     port map ( a0  => a(2),

56                 |al  => a(3),

57                 b0  => b(2),

58                 bl  => b(3),

59                 cin  => cout0_cin1,

60                 cout => cout,

61                 s0  => s(2),

62                 sl  => s(3)

63             );

64

65 end rtl;

```

Figura 3- Código Descrito para 4 bits (continuação)

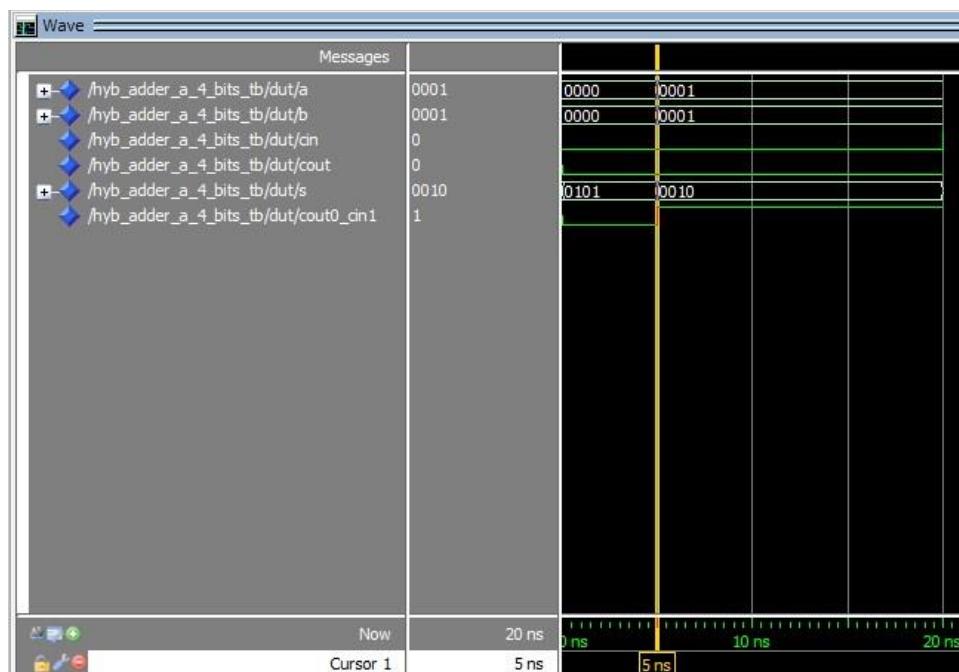

Figura 4- Resultado Obtido

O trabalho, sendo voltado à pesquisa, ainda encontra-se em fase inicial, sendo os primeiros resultados os códigos implementados em linguagem VHDL.

#### 4. CONCLUSÕES

Este é um trabalho em fase inicial de estudo, os resultados apresentados são validações das primeiras etapas, tendo sido realizado a codificação e testes de duas topologias de somadores em código híbrido. Espera-se nas próximas etapas realizar comparações com outras arquiteturas de somadores em síntese ASIC para verificar o consumo de potência das topologias.

## 5. REFERÊNCIAS BIBLIOGRÁFICAS

### Livro

VAHID, Frank. **Sistemas Digitais: projeto, otimização e HDLs.** Porto Alegre: Artmed, 2008. Bookman, 2008.

### Capítulo de livro

VAHID, F. Linguagens de Descrição de Hardware. In: VAHID, F.; **Sistemas Digitais: projeto, otimização e HDLs.** Porto Alegre, Artmed, 2008. Bookman, 2008. Cap. 9, p. 463 –515.

### Artigo

SOBRENOME, Letras Iniciais dos Nomes. Título do Artigo. **Nome da Revista**, Local de Edição, v.?, n.?, p. página inicial - página final, ano da publicação.

Ex.: MEWIS, I.; ULRICHS, C.H. Action of amorphous diatomaceous earth against different stages of the stored product pests *Tribolium confusum*(Coleoptera: Tenebrionidae), *Tenebrio molitor* (Coleoptera:Tenebrionidae), *Sitophilus granarius* (Coleoptera: Curculionidae) and *Plodia interpunctella* (Lepidoptera: Pyralidae). **Journal of Stored Product Research**, Amsterdam, v.37, n.1, p.153-164, 2001.

### Tese/Dissertação/Monografia

COSTA, E.A.C. **Operadores Aritméticos de Baixo Consumo para Arquiteturas de Circuitos DSP.** 2002. Tese (Doutorado em Ciência da Computação) - Programa de pós-graduação em Computação, Universidade Federal do Rio Grande do Sul.

FERREIRA, R.S. **Arquiteturas de Hardware de Baixa Potência para Codificação de Vídeo usando Operadores Aritméticos de Codificação Híbrida.** 2016. Dissertação (Mestrado em Engenharia Eletrônica e Computação) - Mestrado em Engenharia Eletrônica e Computação, Universidade Católica de Pelotas.