## PROJETO DE UM CIRCUITO HÍBRIDO CMOS/MEMRESISTIVO PARA A EXECUÇÃO PREDITIVA DE IMPLICAÇÕES MATERIAIS

CESAR DE SOUZA DIAS<sup>1</sup>; PAULO FRANCISCO BUTZEN<sup>2</sup>

<sup>1</sup>*Universidade Federal do Rio Grande – eng.cesar.dias@gmail.com*

<sup>2</sup>*Universidade Federal do Rio Grande – paulobutzen@furg.br*

### 1. INTRODUÇÃO

Durante as últimas quatro décadas, a indústria de semicondutores tem constantemente buscado a redução das dimensões dos dispositivos que fazem parte dos circuitos integrados. Esta miniaturização leva a uma maior densidade de encapsulamento, circuitos mais rápidos e menor dissipação de potência por operação (TAUR *et al.*, 1997). Infelizmente, está se tornando cada vez mais difícil sustentar esta tendência, uma vez que as dimensões dos MOSFETs já assentam sobre o regime nanométrico (KUHN, 2012). Com os transistores aproximando-se dos limites físicos da atomística e da mecânica quântica, a indústria de semicondutores está enfrentando um enorme desafio técnico, e a predominância da tecnologia CMOS em aplicações VLSI encontra-se ameaçada (LIKHAREV, 2003; WILLIAMS, 2008).

Os problemas com a alta dissipação estática e dinâmica de potência devido às crescentes correntes de fuga e a longa distância física entre os blocos lógicos e de memória têm se tornado obstáculos importantes a serem superados. (KIM *et al.*, 2003). Para minimizar o consumo energético em circuitos VLSI e melhorar o seu desempenho e confiabilidade, a exploração de tecnologias emergentes tem despontado como uma alternativa promissora para o futuro da indústria de semicondutores, em detrimento à árdua continuidade do paradigma tecnológico vigente (JABEUR *et al.*, 2014).

Diante deste quadro, consolidou-se um ambiente favorável para a ascensão dos memristores. O memristor é o quarto elemento fundamental da Eletrônica, cujo nome é uma contração de “Memory Resistor”, em função deste se comportar, de certa forma, como um resistor não linear com memória (CHUA, 1971). Existem diversas aplicações baseadas na utilização destes dispositivos, que incluem memórias não voláteis de alta densidade de integração, circuitos lógicos digitais, circuitos analógicos e até mesmo sistemas neuromórficos. Dentre as abordagens utilizadas para o projeto de circuitos lógicos digitais, encontra-se a implicação material. Sendo assim, o presente trabalho propõe um circuito híbrido CMOS/memresistivo capaz de tornar mais eficiente a síntese de funções booleanas através da utilização desta técnica.

### 2. METODOLOGIA

O desenvolvimento do trabalho compreendeu a descrição elétrica de um circuito para a realização da implicação material memresistiva, usando a linguagem SPICE. Foi utilizado um modelo preditivo de MOSFETs (PTM, 2008) de 45 nm e um modelo elétrico autoral de memristor, adaptado do trabalho de PERSHIN e DI VENTRA (2012). Simulações elétricas foram realizadas no ambiente NGSPICE para realizar a análise da produtividade de operações implicativas em função do valor de tensão elétrica existente no nó comum do circuito utilizado. Com base nos resultados deste experimento, foi possível

idealizar um circuito elétrico para o aprimoramento da eficiência na síntese de funções booleanas através da lógica implicativa.

### 3. RESULTADOS E DISCUSSÃO

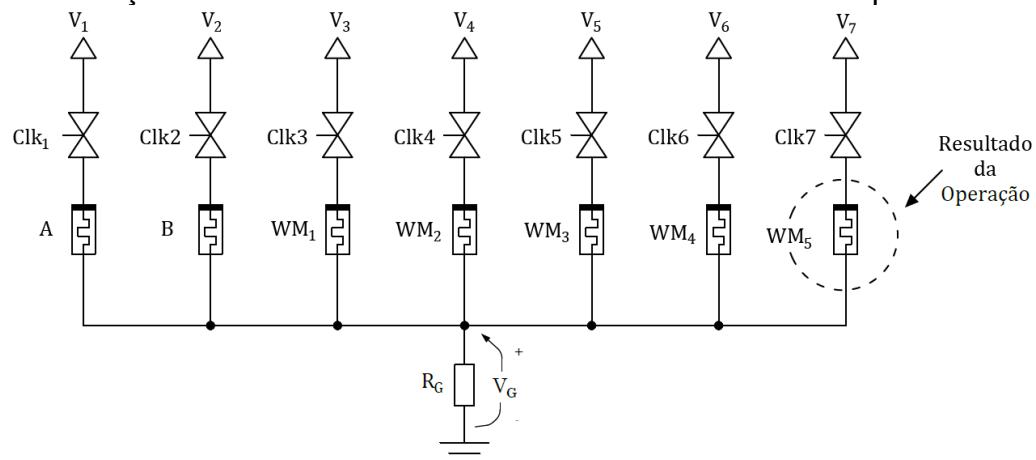

Até o momento, descreveu-se eletricamente o circuito exibido na Figura 1, o qual é similar àquele apresentado por BORGHETTI *et al.* (2010). O arranjo de dispositivos utilizado, no entanto, utiliza portas de transmissão CMOS em série com os memristores para a seleção dos elementos participantes da implicação e para a condução bidirecional de corrente elétrica através dos componentes.

Figura 1. Circuito utilizado para a implementação da implicação material memristiva.

Para a construção deste circuito, foram usados cinco memristores de trabalho, denominados  $WM_1$  a  $WM_5$ , e dois memristores de entrada, A e B. O circuito implementado possibilitou a produção de funções booleanas através da variação dos estados de resistência dos memristores e a monitoração da tensão elétrica no nó  $V_G$  durante a execução de cada uma das implicações. A produção da porta lógica XOR de duas entradas foi escolhida para demonstrar o resultado parcial obtido. Para sintetizar esta função, foi utilizada uma sequência com cinco implicações lógicas, ilustradas na Tabela 1.

Tabela 1. Sequência de implicações para a síntese da função lógica XOR.

| Implicação                          | Lógica executada                                                                 |

|-------------------------------------|----------------------------------------------------------------------------------|

| 1. $A \rightarrow WM_1$             | $WM_1 = \bar{A}$                                                                 |

| 2. $B \rightarrow WM_2$             | $WM_2 = \bar{B}$                                                                 |

| 3. $(A + B) \rightarrow WM_3$       | $WM_3 = \overline{A + B}$                                                        |

| 4. $(WM_1 + WM_2) \rightarrow WM_4$ | $WM_4 = \overline{\bar{A} + \bar{B}}$                                            |

| 5. $(WM_3 + WM_4) \rightarrow WM_5$ | $WM_5 = \overline{\overline{A + B} + \overline{\bar{A} + \bar{B}}} = A \oplus B$ |

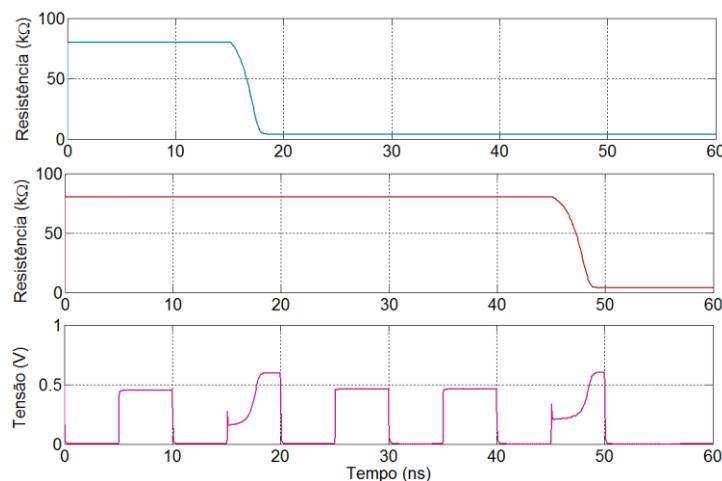

O resultado final da operação é armazenado como a resistência do memristor  $WM_5$ . Dentre os parâmetros de simulação mais relevantes para o levantamento dos dados, foram utilizados os limites de resistências  $R_{ON} = 4\text{k}\Omega$  para o nível lógico '1' e  $R_{OFF} = 80\text{k}\Omega$  para o nível '0'. Todos os memristores de trabalho foram inicializados com o valor de resistência  $R_{OFF}$ . Para a combinação de entrada "10", exibem-se, na Figura 2, os comportamentos temporais das

resistências  $WM_2$  e  $WM_5$ , as únicas a sofrerem alterações em seus estados lógicos iniciais.

Figura 2. Comportamento temporal das resistências do memristores de trabalho  $WM_2$  e  $WM_5$  e tensão  $V_G$ .

Nota-se que a tensão  $V_G$  permanece constante e próxima a 0,5 V nos instantes em que nenhuma alteração ocorre. Por outro lado, no início de operações que alteram o estado de resistência de algum memristor, a tensão encontra-se próxima de 0,2 V. Portanto, consegue-se distinguir a eficácia de uma implicação através da comparação da tensão  $V_G$  com um valor de referência preestabelecido. Da sequência de cinco operações executadas, somente duas delas produziram modificação no estado de algum memristor; as demais foram ineficazes. Em termos percentuais, somente 40% das operações precisariam ser executadas para a geração do resultado esperado. Para as demais combinações de entrada, obtiveram-se os resultados exibidos na Tabela 2:

Tabela 2. Percentual de produtividade das implicações implementadas na síntese da função XOR em função das combinações de entrada.

| A | B | Implicações produtivas (%) |

|---|---|----------------------------|

| 0 | 0 | 60                         |

| 0 | 1 | 40                         |

| 1 | 0 | 40                         |

| 1 | 1 | 20                         |

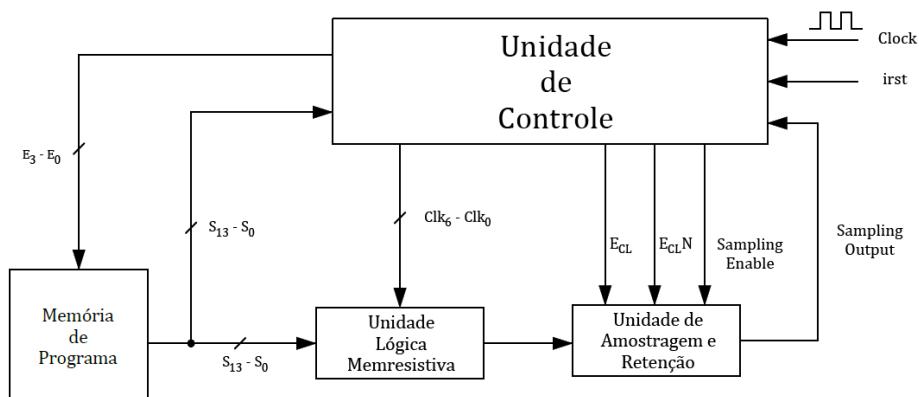

Este padrão de comportamento permitiu que fosse idealizado um circuito capaz de identificar implicações desnecessárias e abreviar expressivamente o tempo de execução destas. Este circuito é constituído por uma memória de programa, uma Unidade Lógica Memresistiva (ULM), uma Unidade de Amostragem/Retenção (UAR) e uma Unidade de Controle (UC). O diagrama em blocos desse arranjo é apresentado na Figura 3.

Nesta arquitetura, Implicações são representadas por palavras de instrução codificadas e armazenadas na memória de programa. Inicialmente estas implicações são buscadas da memória e decodificadas na ULM. Este processo traduz as palavras binárias em níveis de tensão aplicados a cada memristor. A UAR é responsável por comparar a tensão  $V_G$  com um valor de referência, sinalizando a necessidade ou não de execução daquela implicação à UC. Esta ultima é encarregada de gerar sinais de controle para os demais blocos e temporizar a duração da execução de cada operação. Operações desnecessárias

são rapidamente finalizadas, enquanto operações produtivas são mantidas em execução até que a transição de resistência no memristor de trabalho seja concluída.

Figura 3. Circuito híbrido CMOS/memresistivo idealizado para a execução condicional das implicações.

#### 4. CONCLUSÕES

Este trabalho apresentou as ideias que norteiam o projeto de um circuito híbrido CMOS/memresistivo para a execução preditiva de implicações materiais. Acredita-se que a contribuição desta obra se dá no sentido de proporcionar à comunidade científica um circuito apto a realizar concomitantemente a síntese de funções booleanas e o armazenamento de dados, com desempenho superior àquele praticado por circuitos congêneres. Futuramente espera-se concluir o desenvolvimento do circuito e validá-lo, tornando possível a execução automática e condicional das operações implicativas de acordo com a produtividade destas.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

- BORGHETTI, J. et al. 'Memristive' switches enable 'stateful' logic operations via material implication. **Nature**, v. 464, n. 7290, p. 873-876, 2010. ISSN 0028-0836.

- CHUA, L. Memristor-The missing circuit element. **IEEE Transactions on Circuit Theory**, v. 18, n. 5, p. 507-519, 1971. ISSN 0018-9324.

- JABEUR, K.; DI PENDINA, G.; PRENAT, G. Ultra-energy-efficient CMOS/magnetic non-volatile flip-flop based on spin-orbit torque device. **Electronics Letters**, v. 50, n. 8, p. 585-587, 2014. ISSN 1350-911X.

- KIM, N. S. et al. Leakage current: Moore's law meets static power. **computer**, v. 36, n. 12, p. 68-75, 2003. ISSN 0018-9162.

- KUHN, K. J. Considerations for Ultimate CMOS Scaling. **IEEE Transactions on Electron Devices**, v. 59, n. 7, p. 1813-1828, 2012. ISSN 0018-9383.

- LIKHAREV, K. Electronics below 10 nm. **Nano and Giga Challenges in Microelectronics**, p. 27-68, 2003.

- PERSHIN, Y. V.; DI VENTRA, M. SPICE model of memristive devices with threshold. **arXiv preprint arXiv:1204.2600**, 2012.

- PTM. Predictive Technology Model. 2008. Disponível em: <<http://ptm.asu.edu/>>.

- TAUR, Y. et al. CMOS scaling into the nanometer regime. **Proceedings of the IEEE**, v. 85, n. 4, p. 486-504, 1997. ISSN 0018-9219.

- WILLIAMS, R. S. How we found the missing memristor. **IEEE spectrum**, v. 45, n. 12, 2008. ISSN 0018-9235.