## PROJETO E SÍNTSE DE ARQUITETURAS DE HARDWARE DEDICADAS PARA A FERRAMENTA DEPTH INTRA SKIP DO PADRÃO 3D-HEVC

MARIANA UCKER<sup>1,2</sup>; VLADIMIR AFONSO<sup>1,2</sup>; MARCELO PORTO<sup>2</sup>; LUCIANO AGOSTINI<sup>2</sup>

<sup>1</sup>Instituto Federal Sul-rio-grandense – Campus Pelotas

<sup>2</sup>Universidade Federal de Pelotas – Video Technology Research Group (ViTech)

{mariana.ucker<sup>1,2</sup>, vafonso<sup>1,2</sup>, porto<sup>2</sup>, agostini<sup>2</sup>}@inf.ufpel.edu.br

### 1. INTRODUÇÃO

Vídeos 3D tornam a experiência de visualização dos espectadores mais realista ao custo de um aumento considerável na quantidade de bits necessários para representar um vídeo. O padrão HEVC (*High Efficiency Video Coding*) define uma extensão, chamada 3D-HEVC, que permite o processamento de uma quantidade maior de imagens para um mesmo instante de tempo quando comparado ao modelo de codificação normalmente aplicado para vídeos 2D. O 3D-HEVC utiliza o conceito MVD (*Multi-View plus Depth*), onde cada vista de textura que compõe o vídeo 3D é associada a um mapa de profundidade, que apresenta a distância dos objetos em relação à câmera (TECH, 2016). Com isso, além de explorar as redundâncias espacial, temporal e de disparidade, que já eram exploradas em padrões anteriores, como o H.264/MVC (SULLIVAN, 2012), o 3D-HEVC também introduziu novas ferramentas de codificação específicas para a codificação dos mapas de profundidade. Por esse motivo, há um aumento significativo da complexidade computacional na codificação de vídeos usando o 3D-HEVC.

De acordo com AHMAD et al. (2015), o modelo de renderização é a parte da arquitetura do codificador do 3D-HEVC que exige o maior esforço computacional. Este modelo de renderização é formado basicamente pelo Inicializador, pelo Re-renderizador parcial e pelo cálculo do SVDC (*Synthesized View Distortion Change*), o qual faz a soma das distorções ao quadrado. O resultado do SVDC é utilizado pelo DIS (*Depth Intra Skip*) para decidir qual o melhor modo de codificação para um bloco, baseado no RDO (*Rate-Distortion Optimization*) (TECH, 2016).

Visando diminuir o esforço computacional mencionado acima, AFONSO et al. (2017) propôs uma arquitetura que, ao invés de utilizar o modelo de renderizador com SVDC para o cálculo das distorções, utiliza SAD (*Sum of Absolute Differences*), o qual é um critério de similaridade amplamente utilizado na implementação de codificadores baseados no padrão HEVC. Nesse estudo, o autor estima que a potência dissipada é reduzida, visto que o número de operações diminui bastante, além disso, que o aumento do BD-rate (BJONTEGAARD, 2008) é insignificante.

A presente pesquisa tem como objetivos principais implementar as arquiteturas que realizam o cálculo do SVDC e do SAD, e verificar a eficiência da arquitetura proposta por AFONSO et al. (2017) quanto a redução no custo de área em chip e potência dissipada.

### 2. METODOLOGIA

As arquiteturas que fazem os cálculos do SVDC e do SAD foram descritas em VHDL. Além disso, foram implementados os blocos Acumulador e Comparador, para que se obtenha o resultado do melhor modo de predição, ou seja, qual modo deverá ser usado na codificação da ferramenta *Depth Intra Skip*. A síntese para ASIC foi realizada utilizando a ferramenta *Encounter RTL Compiler*, com uma frequência de operação de 50MHz, utilizando a biblioteca *Nangate* para tecnologia de 45nm .

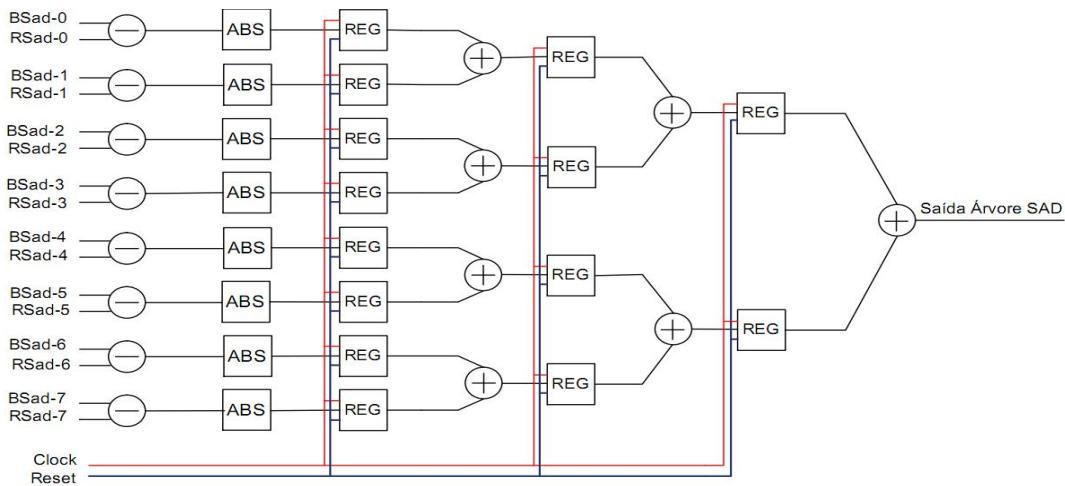

O cálculo do SAD foi feito baseado na equação 1, onde  $S_D$  e  $\tilde{S}_D$  significam a amostra do mapa de profundidade original e reconstruído, respectivamente; e  $(x, y)$  indica a posição da amostra em um dado bloco B (AFONSO, 2017). A arquitetura foi implementada a partir de quatro árvores de SAD, onde cada uma recebe informações de 8x8 bits e fornece um resultado de 11 bits. Como pode ser visto na Figura 1, foram utilizados três níveis de registradores de *pipeline* na estrutura da árvore. O primeiro nível possui oito registradores, os quais recebem como entrada o resultado absoluto da subtração entre os sinais de entrada. O segundo nível possui quatro registradores, onde cada um recebe como entrada o resultado da soma entre a saída de dois registradores do nível anterior. O último nível possui dois registradores apenas e repete a lógica do nível anterior. Por fim, as saídas dos registradores do terceiro nível são somadas, gerando o resultado final da árvore de SAD. Na Figura 1 as entradas BSad e RSad equivalem as variáveis  $S_D$  e  $\tilde{S}_D$  apresentadas na equação 1.

$$SAD = \sum_{(x,y) \in B} |S_D(x, y) - \tilde{S}_D(x, y)| \quad (1)$$

Figura 1 - Árvore de SAD

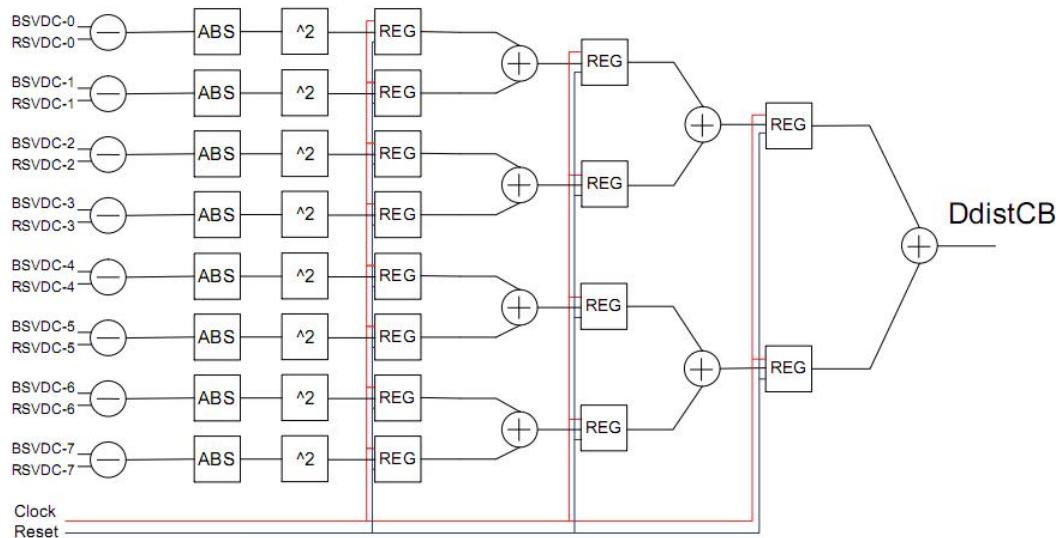

O cálculo do SVDC foi realizado com base na equação 2, onde  $S'_{T,Ref}$  significa uma textura de referência renderizada usando a textura original e o mapa de profundidade original;  $I$  representa o conjunto de todos amostras na vista sintetizada;  $S'_T$  denota uma textura renderizada usando dados de profundidade codificados para blocos já codificados e dados de profundidade originais para outros blocos;  $\tilde{S}_T$  representa uma textura sintetizada com um mapa de profundidade que contém os dados de profundidade distorcidos para o bloco atual (AFONSO, 2017). A arquitetura utilizada para o cálculo do SVDC é muito semelhante à utilizada para o cálculo do SAD, como pode ser visto na Figura 2. Pode-se dizer que existem duas diferenças principais entre as duas arquiteturas. A primeira é que o resultado das subtrações é elevado ao quadrado antes de ir para o primeiro nível de registradores. Além disso, ao invés de utilizar uma árvore são necessárias duas para gerar cada uma das quatro saídas. A primeira árvore tem como sinais de entrada  $\tilde{S}_T$  e  $S'_{T,Ref}$ , já a segunda árvore tem como sinais de entrada as outras duas varáveis, ou seja,  $S'_T$  e  $S'_{T,Ref}$ . A saída é gerada subtraindo o valor de saída da segunda árvore do valor de saída da primeira.

$$SVDC = \sum_{(x,y) \in I} [\tilde{S}_T(x, y) - S'_{T,Ref}(x, y)]^2 - \sum_{(x,y) \in I} [S'_T(x, y) - S'_{T,Ref}(x, y)]^2 \quad (2)$$

Figura 2 - Árvore de SVDC

O acumulador foi implementado utilizando um multiplexador 2x1, um bloco de soma e um registrador. O multiplexador recebe o resultado do cálculo de SAD ou SVDC e sua saída é enviada ao somador, onde é somado com o valor presente na saída. O valor resultante dessa operação é enviado para o registrador, o qual envia o resultado para a saída a cada pulso de *clock*.

O comparador foi implementado de forma que os resultados de SAD ou SVDC sejam comparados dois a dois. O resultado de cada uma das comparações é utilizado para seleção em dois multiplexadores, onde um recebe os dois valores de SAD ou SVDC que foram comparados e o outro recebe os modos relacionados aos mesmos. Após as duas primeiras comparações, os valores que passam pelos multiplexadores são novamente comparados. Desta forma, um multiplexador entrega na saída o melhor valor de SAD ou SVDC e o outro o melhor modo de predição.

### 3. RESULTADOS E DISCUSSÃO

Com a realização das simulações foram obtidos os resultados apresentados na Tabela 1, os quais comprovam a teoria apresentada por AFONSO et al. (2017), como já era esperado.

Na Tabela 2, são apresentados os resultados obtidos na síntese para ASIC. De acordo com essa tabela, a arquitetura que utiliza o SVDC para o cálculo dissipa uma potência aproximadamente 78% maior e ocupa uma área 76% maior quando comparada com a arquitetura que utiliza o SAD. Nesse trabalho a área foi mapeada para o número de Gates considerando portas NAND de duas entradas.

Tabela 1 - Resultados para ASIC

|                     | Arquitetura com SAD | Arquitetura com SVDC | Diferença |

|---------------------|---------------------|----------------------|-----------|

| <b>Power (mW)</b>   | 7,89                | 36,079               | 78%       |

| <b>Área (Gates)</b> | 20887               | 87110                | 76%       |

#### 4. CONCLUSÕES

Este trabalho apresentou os resultados do desenvolvimento de duas arquiteturas de hardware dedicadas para a implementação da ferramenta DIS do padrão de codificação de vídeo 3D-HEVC. As arquiteturas foram desenvolvidas em VHDL e sintetizadas para ASIC (*Application Specific Integrated Circuits*), utilizando a versão 11.1 da ferramenta *Encounter RTL Compiler* e a biblioteca *Nangate* para tecnologia de 45nm.

O desenvolvimento deste trabalho demonstra a eficiência do ponto vista de consumo energético de parte da arquitetura proposta por AFONSO et al. (2017) para o cálculo do critério de similaridade, pois de acordo com os resultados apresentados, a área ocupada e a dissipação de potência são significativamente menores quando comparados a arquitetura que utiliza o SVDC.

Em trabalhos futuros, será feito um estudo aprofundado do funcionamento do modelo de renderizador utilizado na ferramenta *Depth Intra Skip* da extensão 3D-HEVC, para que o mesmo possa ser descrito em VHDL. Além disso, será implementada toda a arquitetura proposta por AFONSO et al. (2017), considerando todos os tamanhos de bloco e não apenas o tamanho 8x8.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

AFONSO, V.; SUSIN, A.; AUDIBERT, L.; SALDANHA, M.; CONCEIÇÃO, R.; PORTO, M.; ZATT, B.; AGOSTINI, L. Low-Power and High-Throughput Hardware Design for the 3D-HEVC Depth Intra Skip. **IEEE International Symposium on Circuits and Systems (ISCAS)**. 2017.

AHMAD, Waqar; MARTINA, Maurizio; MASERA, Guido. Complexity and implementation analysis of synthesized view distortion estimation architecture in 3D High Efficiency Video Coding. In: **3D Imaging (IC3D), 2015 International Conference on**. IEEE, 2015. p. 1-8.

BJONTEGAARD, Gisle. Improvements of the BD-PSNR model, VCEG-AI11. In: **ITU-T Q. 6/SG16, 34th VCEG Meeting, Berlin, Germany (July 2008)**. 2008.

CHEN, Ying; TECH, Gerard; WEGNER, Krzysztof; YEA, Sehoon. Test Model 11 of 3D-HEVC and MV-HEVC. **11th Meeting: Geneva**, CH, 12–18 Feb. 2015

CONCEIÇÃO, R.. **Early Skip/DIS: Uma Heurística para Redução de Complexidade no Codificador de Mapas de Profundidade do 3D-HEVC**. 2016. Dissertação. Programa de Pós-graduação em computação, Universidade Federal de Pelotas.

SULLIVAN, Gary J. et al. Overview of the high efficiency video coding (HEVC) standard. **IEEE Transactions on circuits and systems for video technology**, v. 22, n. 12, p. 1649-1668, 2012.

TECH, Gerhard et al. Overview of the multiview and 3D extensions of high efficiency video coding. **IEEE Transactions on Circuits and Systems for Video Technology**, v. 26, n. 1, p. 35-49, 2016.

TECH, Gerhard et al. Partial Depth Image Based Re-Rendering for Synthesized View Distortion Computation. **IEEE Transactions on Circuits and Systems for Video Technology**, 2016.