## UMA TÉCNICA DE PÓS-PROCESSAMENTO DEDICADA A OTIMIZAÇÃO DE LEIAUTE DE CIRCUITOS INTEGRADOS NA TECNOLOGIA CMOS

**GUSTAVO SMANIOTTO<sup>1</sup>; MAICON CARDOSO<sup>2</sup>; RENATO DE SOUZA<sup>3</sup>

MATHEUS MOREIRA<sup>4</sup>; FELIPE MARQUES<sup>5</sup>; LEOMAR DA ROSA JR.<sup>6</sup>**

*Universidade Federal de Pelotas –*

{*ghsmaniotto<sup>1</sup>, mscardoso<sup>2</sup>, rsdsouza<sup>3</sup>, felipem<sup>5</sup>, leomarjr<sup>6</sup>*}@inf.ufpel.edu.br

<sup>4</sup> *Pontifícia Universidade Católica do Rio Grande do Sul – matheus.moreira@acad.pucrs.br*

### 1. INTRODUÇÃO

A cada dia a tecnologia evolui e os Circuitos Integrados (CIs) tem grande responsabilidade por esta revolução. Novos produtos, plataformas, sistemas são criados para atender melhor o usuário, seja na área da saúde, educação, agricultura, alimentação, transporte, dentre outros. Logo, para esta realidade ser possível, circuitos integrados são utilizados controlar diversas atividades, tendo que coletar e processar os dados vindos de computadores, celulares, micro-ondas, geladeiras, carros, equipamentos de exames médicos, equipamentos agrícolas, etc. Devido a este crescimento, novas maneiras de projetar os CIs são propostas para otimizar os produtos presentes no mercado.

Neste contexto, no projeto de CIs, devemos primeiramente descrever o comportamento (ou lógica) do nosso circuito, gerar uma rede de transistores equivalente a esta lógica, definir o tamanho dos transistores de forma a obedecer às especificações do circuito, posicionar e rotear estes transistores na célula e compactar a mesma respeitando regras de projeto. Este fluxo, faz frente ao fluxo tradicional utilizado na academia e na indústria, no qual são utilizadas células pré-projetadas para construir o circuito final. O fluxo alternativo ao padrão disponibiliza mais flexibilidade ao projetista do circuito (ZHU, 1993).

Baseado neste fluxo, diversos trabalhos estudam maneiras eficientes de gerar uma rede de transistores dada uma equação lógica de entrada. As estratégias estado-da-arte encontradas na literatura são Kernel Finder (KF)(POSSANI, 2015) e Functional Composition (FC)(MARTINS, 2010). Na comparação, a primeira é capaz de gerar redes não-série-paralelo (NSP) e série-paralelo (SP), enquanto FC gera somente redes SP. Vale a pena ressaltar que redes NSP podem possuir algumas propriedades como não-dualidade, não-planaridade, diferente quantidade de transistores P e N, dentre outras, que impactam nos métodos de posicionamento e roteamento de transistores na etapa de geração do leiaute, como demonstrado em Cardoso (2016). Com estas características, na comparação, KF obtém melhores resultados que a ferramenta FC no quesito número de chaves. As duas estratégias geram redes com menor número de transistores comparado com o fluxo padrão, porém, as duas utilizam somente o número de chaves como parâmetro de otimização, não levando em conta o leiaute final.

Sabendo deste detalhe, alguns métodos de reordenar (LENGAUER, 1988) (MUELLER, 1986) (ROY, 2007) os transistores das redes geradas automaticamente já foram propostos na literatura, contudo, estas metodologias são utilizadas apenas em redes SP. Estes trabalhos têm como objetivo encontrar Caminhos de Euler, (partir de uma chave da rede e percorrer todos chaves sem passar duas vezes na mesma chave) nas redes de transistores, objetivando o design otimizado do leiaute final. Logo, sabendo da qualidade dos resultados de KF, que também geram redes NSP, foi proposto neste trabalho uma metodologia de pós-processamento para reordenar os transistores das redes geradas por KF visando gerar um leiaute otimizado.

## 2. METODOLOGIA

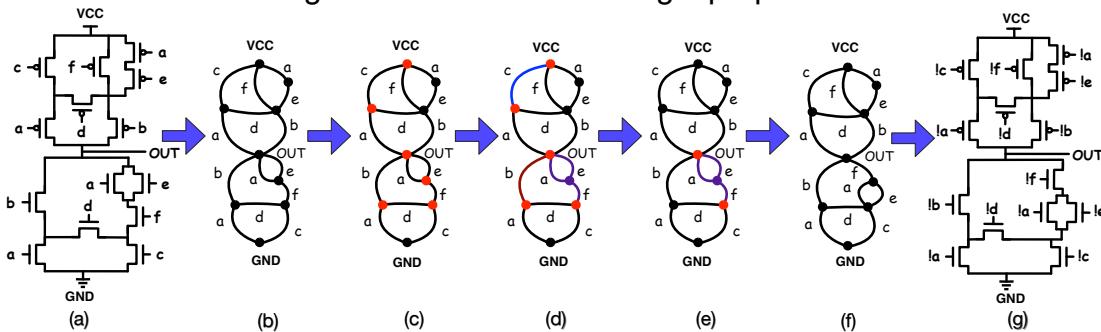

Para solucionar o problema foi proposto um método de pós-processamento que faz uso de uma clássica estrutura de dados nomeada grafos, formada por nodos e arestas. Para este caso específico, a rede de transistores (Fig. 1(a)) é representada por um grafo (Fig. 1(b)), na qual cada aresta representa um transistor e cada nodo representa um terminal do transistor. A metodologia proposta para solucionar o problema é ilustrada pela Fig. 1.

Dada a Fig. 1, o primeiro passo da metodologia consiste em utilizar uma rede que foi gerada automaticamente a partir de uma função lógica (utilizando KF ou FC como gerador automático) e converte-la em um grafo (Fig. 1(a) e (b)). Utilizando o grafo, é preciso procurar todos nodos ímpares (nodos que possuem um número ímpar de arestas conectadas a ele), este passo é detalhado na Fig. 1(c) (os nodos ímpares estão destacados em vermelho). Após identificar estes nodos é necessário encontrar todos os caminhos entre todos nodos. Alguns dos caminhos são destacados na Fig. 1(d), porém é necessário encontrar todos caminhos possíveis entre todos os nodos, para dar início a próxima fase.

Fig. 1 – Fluxo da metodologia proposta

Na sequencia, será necessário analisar cada caminho encontrado de modo que a inversão de todo caminho modifique o grau dos nodos, gerando mais nodos pares e menos nodos ímpares em toda rede. Esta etapa pode ser vista na Fig. 1(e) na qual foi selecionado um dos caminhos encontrados e na Fig. 1(f) esta representada a inversão do caminho citada acima. Logo, na Fig. 1(f) podemos notar que a inversão do caminho reduziu o número de nodos ímpares, o que é desejado para criação de Caminhos de Euler. Por outro lado, caso a inversão do caminho seja inválida (altere a lógica do circuito) ou não altere o grau dos nodos, a inversão já realizada é cancelada e desta forma o grafo da rede volta ser o grafo Fig. 1(e). Finalizando, na Fig. 1(g) temos a rede resultante aplicando método proposto.

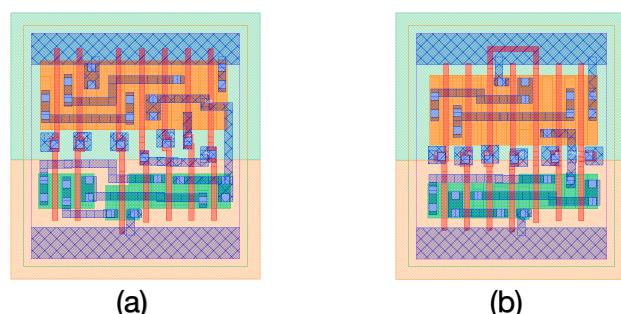

Fig. 2 – (a) Leiaute da rede ilustrada na Fig. 1(a); e (b) leiaute da rede ilustrada na

Fig. 1(g)

O resultado de aplicar esta metodologia pode ser conferido no resultado final de todo fluxo de design de circuitos integrados, o leiaute. Na Fig. 2 são ilustrados os leiautes das redes ilustradas na Fig. 1(a) e (g). Nota-se que o leiaute da rede reordenada possui otimizações em relação ao leiaute original.

### 3. RESULTADOS E DISCUSSÃO

Para avaliar a qualidade do método proposto foram usadas 4 funções para realizar um estudo de caso e verificar a qualidade do método proposto. Assim sendo, as redes foram geradas pela ferramenta KF, os transistores das redes foram dimensionados utilizando a estratégia Logical Effort (SUTHERLAND, 1998) e as redes foram repassadas como entrada para ferramenta ASTRAN (ZIESEMER, 2014) que é responsável por gerar os leiautes dada a rede de transistores. Após as gerações, foram realizados experimentos para analisar as propriedades elétrica e geométrica de cada uma das células.

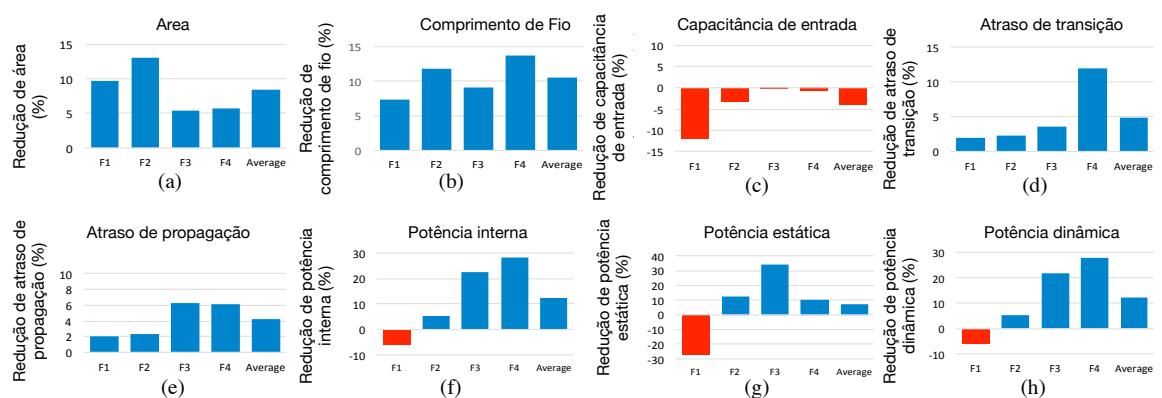

O estudo de caso comparou o leiaute da rede original e o leiaute da rede com o pós-processamento aplicado e os resultados deste estudo estão detalhados na Fig. 3. Nos gráficos, barras vermelhas representam perdas geradas pelo método proposto e as barras em azul representam otimizações geradas pelo método, sendo estes valores porcentagens.

Os dois primeiros aspectos analisados foram área (Fig. 3(a)) e comprimento de fio (Fig. 3(b)), nos quais obteve-se ganho aplicando o método proposto, em média cerca de 9% e 10% de redução de área e comprimento de fio. Nos aspectos elétricos o método proposto reduziu o tempo de atraso de transição (Fig. 3(d)) e de propagação (Fig. 3(e)) em 5% e 4% respectivamente. Da mesma forma, nos quesitos de potência interna (Fig. 3(f)), estática (Fig. 3(g)) e dinâmica (Fig. 3(h)) o pós-processamento proposto gerou uma otimização de em média 10%, 8% e 12%, respectivamente. O único quesito em que não obtivemos ganho aplicando o método proposto foi na capacidade de entrada (Fig. 3(c)), no qual gerou-se uma perda de em média 4%.

Fig. 3 – Resultados da avaliação elétrica e geométrica

Os resultados do estudo de caso são alcançados aplicando a metodologia proposta, que não utiliza uma abordagem de analisar todos caminhos possíveis, ao contrário, o método faz modificações pontuais na rede de transistores em locais de prováveis otimizações (nodos com grau ímpar). Além disso, a metodologia proposta otimiza tanto redes SP quanto redes NSP, o que as metodologias anteriores não consideravam.

## 4. CONCLUSÕES

Conclui-se deste trabalho que é possível otimizar os leiautes de redes de transistores geradas automaticamente por ferramentas estado-da-arte (FC e KF), tendo em vista que estas metodologias de geração não consideram o aspecto leiaute durante a geração das redes, somente consideram a redução do número de chaves. Analisando o estudo de caso realizado é possível ver viabilidade no método, pois além de gerar bons resultados, o pós-processamento realizado não impacta na lógica do circuito e aplica modificações pontuais na rede, evitando uma estratégia exaustiva para a resolução do problema.

Como trabalho futuro pretende-se fazer o mesmo experimento para um conjunto maior de células para verificar sua real viabilidade, além de ser necessário aplicar esta metodologia circuitos digitais reais.

## 5. REFERÊNCIAS BIBLIOGRÁFICAS

ZHU, J., et. al. "On the optimization of MOS circuits". **IEEE Trans. on Circuits and Systems I: Fundamentals, Theory and Applications**. vol. 40, no. 6, pp. 412-422. 1993.

KAGARIS, D., et. al. "A Methodology for Transistor-Efficient Supergate Design". **IEEE Transactions on Very Large Scale Integration (VLSI) Systems**. vol. 15, no. 4. 2007.

MARTINS, A., et. al. "Boolean factoring with multi-objective goals". **2010 IEEE International Conference on Computer Design (ICCD)**. pp.229-234. 2010.

POSSANI, V., et. al. "Graph-based transistor network generation method for supergate design". **IEEE Transactions on Very Large Scale Integration (VLSI) Systems**. no. 99. 2015.

CARDOSO, M. S., et. al. "Topological characteristics of logic networks generated by a graph-based methodology". **2016 IEEE 7th Latin American Symposium on Circuits and Systems (LASCAS)**. pp. 343-346. 2016.

ROY, K. "Optimum Gate Ordering of CMOS Logic Gates Using Euler Path Approach: Some Insights and Explanations". **Journal of Computing and Information Technology**. vol. 15, no. 1, pp. 85-92. 2007.

SUTHERLAND, I., et. al. **Logical Effort: Designing Fast CMOS Circuits**. 1<sup>a</sup> ed., vol. 1. Morgan Kaufmann Publishers Inc., pp. 41-57. 1998.

ZIESEMER, M. A., et. al. "Simultaneous Two-Dimensional Cell Layout Compaction Using MILP with ASTRAN". **2014 IEEE Computer Society Annual Symposium on VLSI**. 2014.

LENGAUER, T., et. al. "Linear algorithms for optimizing the layout of dynamic CMOS cells". **IEEE Transactions on Circuits and Systems**. pp.279-285. 1988.

MUELLER, R., et. al. "Linear Algorithms for Two CMOS Layout Problems". **Proc. of the Aegean Workshop on Computing on VLSI Algorithms and Architectures**. 1986.