## ESTUDO SOBRE A PRECISÃO DAS ESTIMATIVAS DE DISSIPAÇÃO DE POTÊNCIA NA SÍNTESE ASIC COM DIFERENTES METODOLOGIAS

MURILO PERLEBERG; JONES GOEBEL; LUCIANO AGOSTINI;

MARCELO PORTO; BRUNO ZATT

*Universidade Federal de Pelotas – Grupo de Arquiteturas e Circuitos Integrados*

*{mrperleberg, jwgoebel, agostini, porto, zatt}@inf.ufpel.edu.br*

### 1. INTRODUÇÃO

Devido a atual popularização dos dispositivos eletrônicos portáteis, como *smartphones*, *tablets* e câmeras digitais, existe uma grande demanda por dispositivos que combinem certas características de funcionamento, como baixo consumo de energia e elevada taxa de processamento. Desta forma, muitos destes dispositivos portáteis possuem aceleradores de hardware embarcados a fim de atingir taxas de processamento elevadas, como é necessário, por exemplo, nos codificadores e decodificadores de vídeo de alta definição. Portanto, os projetos de hardware vêm se tornando cada vez mais complexos devido à agregação de novas funcionalidades em um único *chip*.

Para proporcionar um maior controle sobre a implementação de um projeto de hardware dedicado e fornecer mais opções no espaço de soluções de acordo com os requisitos de *performance*, consumo energético e tamanho do circuito, os projetistas utilizam os fluxos de síntese ASIC (*Application Specific Integrated Circuit*). O fluxo de síntese ASIC tem como base configurações pré-definidas para as simulações, que contemplam parâmetros como frequência, níveis de otimização em termos de dissipação de potência e utilização de recursos de hardware, entre outros.

Devido a estas configurações, os projetistas além de se preocuparem com a área e o desempenho do circuito, também devem manter a atenção voltada à potência dissipada pela arquitetura em seu regime de funcionamento. Desta modo, as estimativas de dissipação de potência devem ser realizadas considerando os diferentes cenários em que a arquitetura poderá ser utilizada, bem como as características da ferramenta utilizada para a geração da síntese da arquitetura.

As estimativas de dissipação de potência feitas com auxílio das ferramentas de síntese ASIC podem ser realizadas de diversas formas, como utilizando o valor padrão de chaveamento da ferramenta, ou definindo o valor do chaveamento das entradas através da configuração de parâmetros, ou ainda pela utilização de um arquivo que contenha a atividade de chaveamento da arquitetura, gerado a partir de entradas reais do sistema (LANDMAN, 1996) (AHUJA, 2009). A *Atividade de Chaveamento* é a configuração responsável pela geração dos sinais de dados internos, sendo que este parâmetro tem contribuição direta na estimativa da dissipação de potência da arquitetura. Para estimar a dissipação de potência de uma arquitetura de forma mais precisa, os projetistas devem utilizar um arquivo de chaveamento baseado em um cenário real de funcionamento da arquitetura.

Este trabalho tem como objetivo apresentar um estudo sobre alguns fluxos para ferramentas de síntese ASIC comumente utilizados pelos projetistas de hardware para estimar a potência dissipada por uma arquitetura de hardware.

## 2. METODOLOGIA

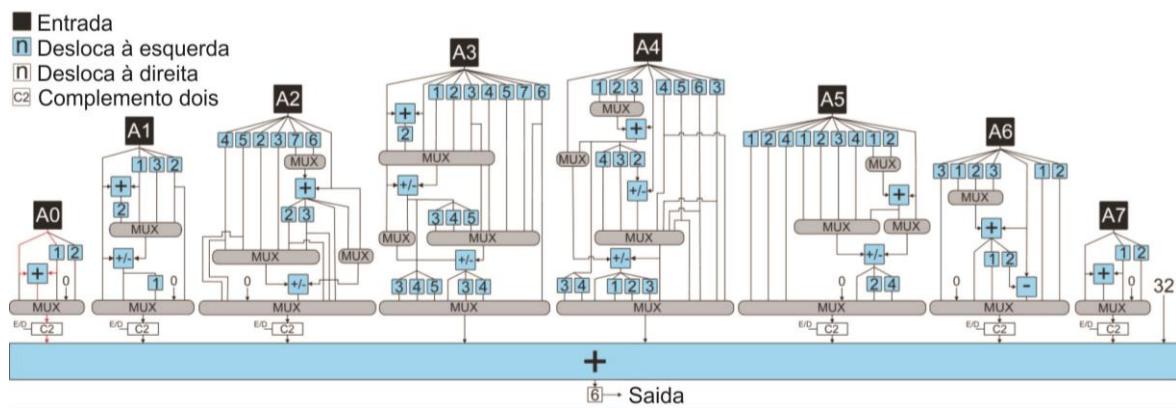

Para a realização do trabalho foram utilizadas duas ferramentas da empresa Cadence: o *Encounter RTL Compiler* para realizar a síntese ASIC e o *irun* para a geração dos arquivos de chaveamento (CADENCE, 2016). Para permitir os experimentos, foram extraídos resultados de estimativa de dissipação de potência utilizando o arquivo de chaveamento *Value Change Dump* (VCD) para uma arquitetura de um filtro utilizado no interpolador dos padrões de codificação de vídeo VP9 e VP10, desenvolvido por membros do grupo GACI em trabalhos anteriores. Na Figura 1, o diagrama de blocos da arquitetura do filtro utilizado nas simulações é apresentado. O filtro tem como objetivo multiplicar cada valor de amostra de entrada (sinais A<sub>0</sub>-A<sub>7</sub>) por diferentes constantes, de acordo com a configuração selecionada. Na verdade, o filtro pode ser configurado para desempenhar quatro tipos de filtragem diferentes: *Legrange*, *Bilinear*, *DCT* e *Smooth*.

**Figura 1** – Arquitetura do filtro dos padrões de codificação de vídeo VP9 e VP10.

Os experimentos foram realizados para cinco métodos distintos. Os dois primeiros métodos contemplam a realização da síntese ASIC para os arquivos HDL, que fazem a descrição *Register Transfer Level* (RTL) do circuito, e para o *netlist* da arquitetura, que foi extraído após a execução da síntese do RTL da arquitetura. Para ambos, a estimativa de dissipação de potência foi realizada utilizando o chaveamento padrão fornecido pela ferramenta *Encounter RTL Compiler*, que é de 20%. Cabe ressaltar que este primeiro método (RTL + chaveamento padrão) é a forma utilizada na maioria dos artigos publicados na literatura atualmente para a geração de estimativas de dissipação de potência em projetos de hardware dedicados.

No terceiro método, a síntese foi realizada utilizando o RTL e o arquivo de atividade de chaveamento que foi gerado utilizando o RTL e o *testbench* da arquitetura, a partir da ferramenta *irun*. O quarto método extrai o *netlist* após a síntese do RTL do circuito para, juntamente com o *testbench*, ser utilizado na geração de um novo arquivo de chaveamento VCD. Então, a síntese com o *netlist* e o novo arquivo VCD é realizada. O *netlist* traz informações mais detalhadas do circuito, o que possibilita uma estimativa mais precisa da dissipação de potência. Nestes métodos foram utilizadas entradas reais, extraídas a partir do software de referência do padrão VP9 (CHROMIUM, 2016) para o vídeo *BasketballDrill* usando a resolução de 832x480 pixels, para a geração dos arquivos VCD. Estes testes foram realizados utilizando 80 mil, 800 mil, 4 milhões e 8 milhões de amostras reais.

O último método se difere dos métodos anteriores, pois utiliza o valor médio do chaveamento de cada pino do circuito, valor este obtido durante a simulação

do quarto método, o qual utiliza o *netlist* e o arquivo de chaveamento. Este valor médio do chaveamento é configurado na ferramenta *Encounter RTL Compiler* e, então, sintetizado juntamente com o RTL da arquitetura.

### 3. RESULTADOS E DISCUSSÃO

A arquitetura do filtro do interpolador dos padrões de codificação de vídeo VP9 e VP10 foi descrita em Verilog HDL e sintetizada para uma biblioteca de 45nm (0.95V) da Nangate (NANGATE, 2016) a uma frequência de 100 MHz utilizando a ferramenta *Encounter RTL Compiler* para obtenção das estimativas de potência. A área obtida durante as simulações foi de 11772,235 $\mu\text{m}^2$ , o que resulta em 14,715K portas *Nand2*, e a potência estática obtida foi de 59 $\mu\text{W}$ . A Tabela 1 apresenta as estimativas de dissipação de potência dinâmica (em micro-watts) obtidas durante a realização da síntese ASIC para todos os métodos verificados.

**Tabela 1** – Resultados de potência dinâmica em ( $\mu\text{W}$ ) de acordo com o método utilizado.

| Método                                                    | Número de amostras (k) |     |      |      |

|-----------------------------------------------------------|------------------------|-----|------|------|

|                                                           | 80                     | 800 | 4000 | 8000 |

| Primeiro (RTL + Chaveamento padrão)                       | 369                    |     |      |      |

| Segundo ( <i>netlist</i> + Chaveamento padrão)            | 364                    |     |      |      |

| Terceiro (RTL + Arquivo VCD do RTL)                       | 220                    | 168 | 166  | 170  |

| Quarto ( <i>netlist</i> + Arquivo VCD do <i>netlist</i> ) | 346                    | 269 | 226  | 229  |

| Quinto (RTL + Chaveamento médio)                          | 347                    | 270 | 270  | 267  |

Comparando a estimativa obtida para os métodos que utilizam o chaveamento padrão e o método que utiliza um arquivo de chaveamento gerado com o *netlist* para 8 bilhões de amostras, vemos que utilizando o chaveamento padrão para o RTL e para o *netlist*, obtivemos uma estimativa que é, respectivamente, 61,13% e 58,95% maior do que a apresentada pelo método que utiliza o arquivo de chaveamento para o *netlist*. Esta diferença, de aproximadamente 60%, ocorre pois o chaveamento padrão do *Encounter RTL Compiler* é de 20%, e o chaveamento obtido utilizando as entradas reais da arquitetura em regime de funcionamento (*netlist* + entradas reais) foi de 11,95% utilizando as 8 bilhões de amostras. Desta forma, a dissipação de potência é superestimada com a utilização do chaveamento padrão da ferramenta ao invés de um arquivo de chaveamento baseado nas entradas reais da arquitetura em regime de funcionamento.

A quantidade de acerto das redes internas da arquitetura no terceiro método, utilizando o RTL e o *testbench* para gerar o arquivo de atividade de chaveamento, foi de apenas 58,45% enquanto que no quarto método, utilizando o *netlist* e o *testbench* para gerar o arquivo de chaveamento, foi obtido 99,96% de acerto nas redes. Sendo assim, as estimativas de dissipação de potência obtidas para o terceiro método apresentam um valor 25,76% menor em relação ao obtido no quarto método. Esta diferença ocorre devido aos erros nas redes, pois a ferramenta infere 0% de chaveamento para redes não acertadas, o que ocorre em 41,55% das redes no terceiro método, e apenas em 0,04% no quarto método.

Nas simulações realizadas com o quarto método foi obtido um valor médio do chaveamento para todas as entradas da arquitetura de 15,95%, 12,21%, 11,99% e 11,95% para as quantidades de 80 mil, 800 mil, 4 milhões e 8 milhões de amostras, respectivamente, de acordo com a ferramenta *Encounter RTL Compiler*. Por meio do quinto método, o qual utiliza o *netlist* e estes valores

médios de chaveamento para configurar manualmente o chaveamento do circuito, foi possível obter uma estimativa da dissipação de potência muito próxima da que foi obtida pelo quarto método, mesmo sem utilizar um arquivo de atividade de chaveamento. Porém, para utilizá-lo, é necessário possuir um bom conhecimento da arquitetura para saber quais portas possuem uma atividade de chaveamento maior ou menor do que outras, como por exemplo, saber a diferença entre o chaveamento das portas de dados, de controle e de reset para configurar o chaveamento de cada uma delas.

Se compararmos os resultados obtidos para o consumo total da arquitetura utilizando 80 mil amostras e 800 mil amostras veremos que os resultados possuem uma grande diferença. Comparando os resultados obtidos para as quantidades maiores do que 800 mil amostras foi possível verificar que, para este filtro do interpolador dos padrões VP9 e VP10, as estimativas da dissipação de potência do circuito começam a estabilizar. Logo, é possível afirmar que, para estimativas mais precisas sobre a dissipação de potência em arquiteturas dos filtros de interpolação dos padrões VP-9 e VP-10, um número mínimo de 800 mil amostras reais de entrada devem ser consideradas.

#### 4. CONCLUSÕES

Este trabalho apresentou uma comparação entre diferentes métodos utilizados para a estimativa da dissipação de potência considerando uma arquitetura do filtro de interpolação dos padrões de codificação de vídeo VP9 e VP10. Os resultados obtidos demonstraram que existe uma grande diferença nos resultados da dissipação de potência de acordo com o método utilizado para gerar esta estimativa. Este estudo demonstrou que as estimativas geradas com o percentual de chaveamento padrão das ferramentas de síntese gera resultados superestimados, de até 60%. Os resultados também mostraram que o método que utiliza o *netlist* e um arquivo de chaveamento, que considere as entradas reais que serão utilizadas depois que o circuito for fabricado, é o que apresenta uma estimativa de dissipação de potência com maior precisão. Por fim, ainda foi possível identificar a necessidade do uso de um grande número de amostras de entrada, pois um número reduzido de amostras interfere muito nas estimativas de dissipação de potência.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

- LANDMAN, P. High-level power estimation. **IEEE Press**, Piscataway, NJ, EUA, p. 29 – 35, 1996.

- AHUJA, S. Power estimation methodology for a high-level synthesis framework. **10th International Symposium on Quality Electronic Design**, San Jose, CA, EUA, p. 541 – 546, 2009.

- CADENCE. **RTL Compiler Beginner's Guides Available on Cadence Online Support.** Acessado em 09 ago. 2016. Online. Disponível em: [https://community.cadence.com/cadence\\_blogs\\_8/b/ld/archive/2013/11/12/rtl-compiler-beginner-s-guides-available-on-cadence-online-support](https://community.cadence.com/cadence_blogs_8/b/ld/archive/2013/11/12/rtl-compiler-beginner-s-guides-available-on-cadence-online-support)

- CHROMIUM. **Chromium open-source browser project, VP9-10 source code.** Acessado em 08 ago. 2016. Online. Disponível em: <http://git.chromium.org/gitweb/?p=webm/libvpx.git;a=tree;f=vp9;hb=aaf61dfbcab414bfacc3171501be17d191ff8506>

- NANGATE. **NanGate FreePDK45 Open Cell Library.** Acessado em 09 ago. 2016. Online. Disponível em [http://www.nangate.com/?page\\_id=2325](http://www.nangate.com/?page_id=2325)