## Desenvolvimento de uma Arquitetura de Modulação 8-PSK

WILLIAM MEDEIROS<sup>1</sup>; MARCELO ROSSI<sup>2</sup>

<sup>1</sup>Universidade Federal de Pelotas – william.meds@gmail.com

<sup>2</sup>Universidade Federal de Pelotas – marcelo.rossi@ufpel.edu.br

### 1. INTRODUÇÃO

O objetivo deste trabalho é o desenvolvimento de um *hardware* para uma técnica de modulação digital 8-PSK (8 *Phase-Shift Keying*). Este *hardware* é capaz de transmitir quaisquer técnicas M-PSK e M-QAM sem alteração física de sua estrutura para uma taxa de transmissão de até 250kbits/s. Por fim, a estrutura proposta é avaliada através dos resultados alcançados, comparando-os aos valores de fase pré-estabelecidos.

Na comunicação digital o símbolo a ser transmitido pode ser representado por um vetor complexo em que as suas componentes, real e imaginária, são representadas por sinais reais, sendo um em fase “I” (real) e o outro em quadratura “Q” (imaginária). Estas componentes são chamadas dessa forma devido ao eixo da componente imaginária, ou em quadratura, ser deslocado de +90° da componente do eixo real.

Portanto, pode-se representar o eixo em quadratura por um sinal senoidal enquanto o eixo em fase é representado por um sinal cossenoide, mantendo assim a diferença de +90° entre a fase deles. Estes sinais defasados em ±90° também são conhecidos como sinais ortogonais e, por serem ortogonais, eles podem ser somados para gerar um sinal composto na saída que o receptor, ao receber esse sinal composto, consegue identificar as componentes que o geraram. Dessa forma, os valores de amplitude destes dois sinais ortogonais irão determinar a posição do símbolo em uma constelação (AGILENT, 2001).

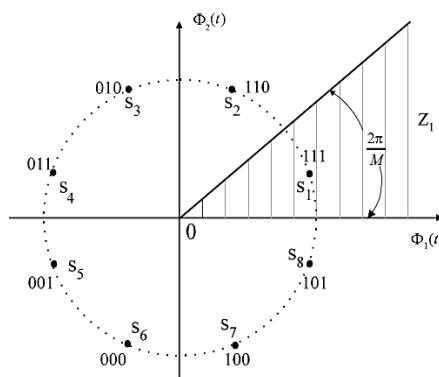

Pode-se dizer, então, que a constelação é um conjunto dos possíveis símbolos que o sinal modulado irá representar em coordenadas polares. Ou seja, a cada instante de tempo o módulo e a fase do sinal representam um único símbolo contido na constelação. A técnica de modulação PSK (*phase-shift keying*) admite qualquer número de fases, porém o 8-PSK é geralmente a ordem mais alta utilizada para a implementação. Isto ocorre devido ao aumento da taxa de erro, que se torna elevado conforme o aumento do número de fases. A modulação 8-PSK é capaz de transformar 3 *bits* em um símbolo, que é a representação de uma de suas oito fases distintas. Cada símbolo da figura 1 representa 3 *bits* que serão transmitidos via variação de fase da portadora. Ou seja, atinge uma taxa de transmissão 3 vezes maior que a modulação BPSK (*binary phase-shift keying*) com a mesma largura de banda (RAPPAPORT, 2008).

### 2. METODOLOGIA

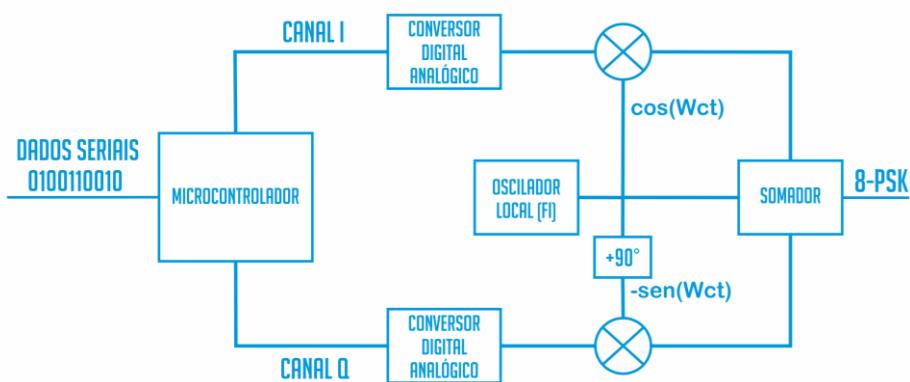

A arquitetura desenvolvida é capaz de transformar sequências de dados digitais em variações na fase de um sinal com frequência intermediária. Para realizar essa tarefa, a arquitetura do *hardware* desenvolvido gera dois sinais ortogonais que são somados para formar um símbolo. Para gerar estes dois sinais ortogonais serão utilizados um oscilador local e um defasador de +90°. Esses sinais ortogonais modulam o sinal que é enviado pelo conversor digital analógico de cada canal. A figura 2 apresenta o diagrama de blocos de

funcionamento do *hardware* que transmite a uma taxa de transmissão de 250kbits/s.

Figura 1 - A constelação da modulação 8-PSK

Fonte: XIONG, 2006, p.150.

Figura 2 - Arquitetura completa do transmissor 8-PSK

Fonte: Autor.

Como a taxa de transmissão do modulador 8-PSK será de 250kbits/s, a interrupção de *timer* do microcontrolador deve ocorrer a cada 4 microssegundos, para obter os *bits* a serem transmitidos que entram de forma serial no microcontrolador e são armazenados em registradores. Como o 8-PSK transmite 3 *bits* por símbolo, a cada três interrupções o microcontrolador deve atualizar os valores em sua saída. As sequências aplicadas nos pinos de saída dependem dos valores armazenados nos registradores, que podemos chamar de Q, I e C. Como são 3 *bits* temos 8 possíveis sequências, visualizadas na tabela 1. Para converter os dados digitais do microcontrolador para um sinal analógico é utilizado um conversor Digital-Analógico e, para isso, utilizou-se o DAC0800, que é capaz de converter 8 *bits* binários nos níveis de tensão adequado à esse projeto.

A fim de gerar a constelação 8-PSK com as 8 fases distanciadas igualmente de 45°, deve-se utilizar os valores que tenham uma relação de aproximadamente 0,414 entre eles. Para o presente projeto utilizou-se  $\pm 82.8\text{mV}$  e  $\pm 200\text{mV}$ .

Tabela 1 - Tensão de saída dos DACs dos canais I e Q

| Q | I | C | Canal I | Canal Q |

|---|---|---|---------|---------|

| 0 | 0 | 0 | -82.8mV | -200mV  |

| 0 | 0 | 1 | -200mV  | -82.8mV |

| 0 | 1 | 0 | -82.8mV | +200mV  |

| 0 | 1 | 1 | -200mV  | +82.8mV |

| 1 | 0 | 0 | +82.8mV | -200mV  |

| 1 | 0 | 1 | +200mV  | -82.8mV |

| 1 | 1 | 0 | +82.8mV | +200mV  |

| 1 | 1 | 1 | +200mV  | +82.8mV |

Seguindo esse procedimentos o posicionamento dos símbolos na constelação para a modulação 8-PSK terá as seguintes fases:  $\pi/8$  (22,5°),  $3\pi/8$  (67,5°),  $5\pi/8$  (112,5°),  $7\pi/8$  (157,5°),  $9\pi/8$  (202,5°),  $11\pi/8$  (247,5°),  $13\pi/8$  (292,5°),  $15\pi/8$  (337,5°).

Um oscilador *Colpitts* foi utilizado como oscilador local, definindo a frequência Intermediaria (IF) em 1.06MHz que será utilizado no canal em fase (I). Para gerar o sinal que será utilizado no canal em quadratura (Q) foi desenvolvido um filtro passa tudo, capaz de defasar o sinal vindo do oscilador *Colpitts* em +90° sem alterar a sua amplitude.

A fim de realizar a multiplicação em ambos canais é utilizado o circuito integrado NE/SA602A. Este circuito é utilizado para multiplicar o sinal em banda base vindo do conversor digital analógico do canal em fase e o sinal do oscilador *Colpitts*, que gera a frequência intermediária. Já para o canal em quadratura, a multiplicação ocorre entre o sinal que chega do conversor digital analógico do canal em quadratura e o sinal vindo do deslocador de fase.

Por fim, um circuito somador irá somar os sinais vindos dos multiplicadores para gerar o símbolo. Para isso foi utilizado um circuito somador não inversor, que foi desenvolvido utilizando um amplificador operacional. Duas entradas do somador são utilizadas para somar o sinal do canal em fase e o em quadratura, obtendo o sinal 8-PSK. Já a outra entrada desse somador serve para transmitir junto ao sinal 8-PSK a onda portadora síncrona não modulada, que será utilizada para realizar a demodulação síncrona no receptor. A tabela 2 mostra o resultado da soma do sinal do canal em fase com o sinal do canal quadratura, sendo 'A' a amplitude de pico a pico do sinal 8-PSK.

Tabela 2 - Formação do sinal 8-PSK

| QIC | Sinal canal I              | Sinal Canal Q              | Sinal 8-PSK                        |

|-----|----------------------------|----------------------------|------------------------------------|

| 111 | $+0.2 \cos(2\pi f_c t)$    | $+0.0828 \sin(2\pi f_c t)$ | $A \cos(2\pi f_c t + 22.5^\circ)$  |

| 110 | $+0.0828 \cos(2\pi f_c t)$ | $+0.2 \sin(2\pi f_c t)$    | $A \cos(2\pi f_c t + 67.5^\circ)$  |

| 010 | $-0.0828 \cos(2\pi f_c t)$ | $+0.2 \sin(2\pi f_c t)$    | $A \cos(2\pi f_c t + 112.5^\circ)$ |

| 011 | $-0.2 \cos(2\pi f_c t)$    | $+0.0828 \sin(2\pi f_c t)$ | $A \cos(2\pi f_c t + 157.5^\circ)$ |

| 001 | $-0.2 \cos(2\pi f_c t)$    | $-0.0828 \sin(2\pi f_c t)$ | $A \cos(2\pi f_c t + 202.5^\circ)$ |

| 000 | $-0.0828 \cos(2\pi f_c t)$ | $-0.2 \sin(2\pi f_c t)$    | $A \cos(2\pi f_c t + 247.5^\circ)$ |

| 100 | $+0.0828 \cos(2\pi f_c t)$ | $-0.2 \sin(2\pi f_c t)$    | $A \cos(2\pi f_c t + 292.5^\circ)$ |

| 101 | $+0.2 \cos(2\pi f_c t)$    | $-0.0828 \sin(2\pi f_c t)$ | $A \cos(2\pi f_c t + 337.5^\circ)$ |

### 3. RESULTADOS E DISCUSSÃO

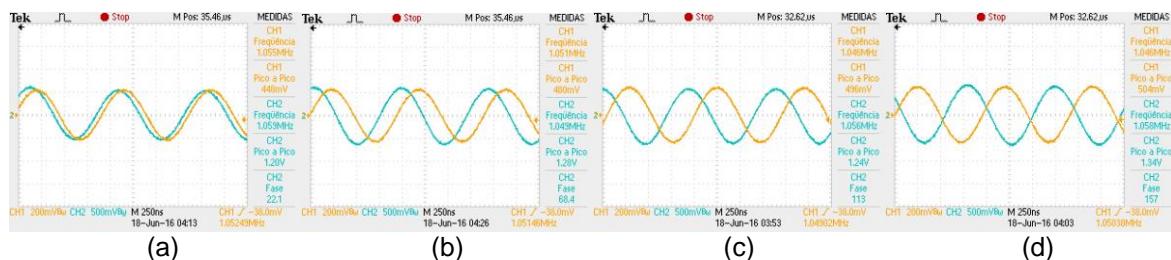

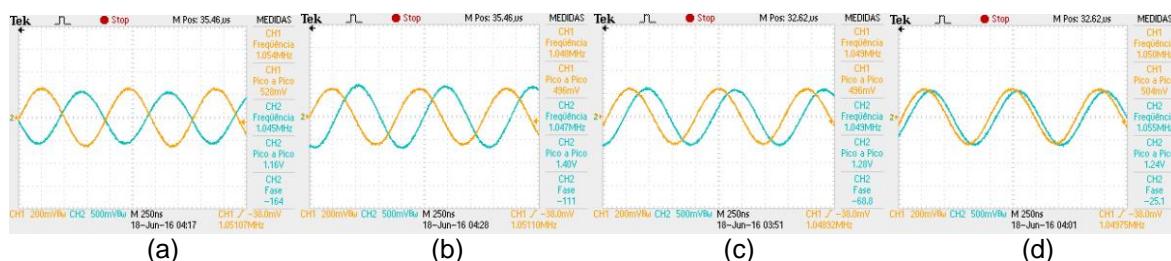

A fim de observar o funcionamento da implementação prática do modulador digital 8-PSK, uma análise foi realizada na etapa final do circuito com o auxílio de um osciloscópio digital. Após somar os sinais de saída dos multiplicadores de ambos canais, é gerado o sinal 8-PSK. Este sinal possui oito variações de fase, portanto iremos verificar cada um desses sinais na saída do somador. Os valores

dos componentes de cada canal que geram os resultados apresentados nas figuras 3 e 4 podem ser visualizados na tabela 2, assim como a sequência binária e a fase resultante da combinação. A Figura 3 e 4 apresenta em azul o sinal 8-PSK e em laranja o sinal de referência.

Figura 3 – Sinal 8-PSK: (a) Representa a fase de  $+22.5^\circ$  (b) fase de  $+67.5^\circ$  (c) fase de  $+112.5^\circ$  e (d) fase de  $+157.5^\circ$

Figura 4 – Sinal 8-PSK: (a) Representa a fase de  $+202.5^\circ$  (b) fase de  $+247.5^\circ$  (c) fase de  $+292.5^\circ$  e (d) fase de  $+337.5^\circ$

## 4. CONCLUSÕES

O hardware desenvolvido para a modulação 8-PSK pode operar tanto para modulações M-PSK quanto para M-QAM sem qualquer alteração física. Sendo assim, ele foi testado para a modulação 8-PSK e a alteração entre essas duas técnicas de modulação pode ser realizada através da modificação do código gravado no microcontrolador ATmega328p. Os valores de fase obtidos na saída do modulador são muito próximos aos valores teóricos apresentados na tabela 2 demonstrando um correto funcionamento do circuito desenvolvido.

Para aplicações específicas onde sejam necessárias uma taxa de transmissão superior a 250kbits/s uma otimização do código pode ser testada ou ser realizada a troca do microcontrolador por um mais veloz, visto que o atmega328p é um microprocessador de baixo custo e tem suas limitações. Para menores taxas de transmissão, apenas uma alteração no tempo de estouro do *timer0* do código é necessária.

## 5. REFERÊNCIAS BIBLIOGRÁFICAS

RAPPAPORT, Theodore S. **Wireless Communications: Principles and Practice.** 2.ed. Massachusetts: Prentice Hall, 2008.

XIONG, Fuqin. **Digital Modulation Techniques.** 2.ed. Norwood: Artech House Publishers, 2006.

### Internet

AGILENT, **Digital Modulation in Communications Systems: An Introduction.** United States of America, 2001. Acessado em 12 jan. 2016. Online. Disponível em: <http://cp.literature.agilent.com/litweb/pdf/5965-7160E.pdf>