## SÍNTESE DE PORTAS LÓGICAS COMPLEXAS GERADAS POR UM PARADIGMA DE MINIMIZAÇÃO DE REDES DE TRANSISTORES BASEADA EM GRAFOS

MAICON S. CARDOSO<sup>1</sup>; GUSTAVO H. SMANIOTTO<sup>1</sup>; REGIS ZANANDREA<sup>1</sup>;

MATHEUS T. MOREIRA<sup>2</sup>; LEOMAR S. DA ROSA JR.<sup>1</sup>; FELIPE DE S. MARQUES<sup>1</sup>

<sup>1</sup>Universidade Federal de Pelotas – Grupo de Arquiteturas e Circuitos Integrados –

{mscardoso, ghsmaniotto, rzanandrea, leomarj, felipem}@inf.ufpel.edu.br

<sup>2</sup>Pontifícia Universidade Católica do Rio Grande do Sul – matheus.moreira@acad.pucrs.br

### 1. INTRODUÇÃO

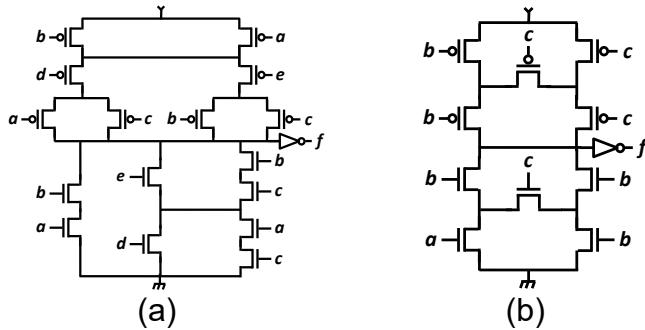

Recentemente, metodologias de minimização de redes de transistores baseadas em grafos vêm ganhando destaque no processo de geração lógica de células sob demanda (KAGARIS, 2007) (POSSANI, 2015). Através de associações não-série-paralelo (NSP) obtidas a partir do compartilhamento de caminhos na célula, esse paradigma gera, em geral, arranjos com um menor número de transistores quando comparados com células série-paralelo (SP) geradas através de metodologias baseadas em fatoração Booleana (GOLUMBIC, 2008) (MARTINS, 2010). A Figura 1 ilustra esse aspecto, onde a função Booleana  $f$  é implementada em duas versões distintas: SP (a) e NSP (b).

Figura 1. Porta complexa  $f$ . (a) Versão SP. (b) Versão NSP.

No entanto, apesar de apresentar otimizações relativas ao número de transistores, as metodologias baseadas em grafos apresentam características topológicas particulares, tais como a ocorrência de não-planaridade e não-dualidade entre os planos lógicos que formam o arranjo. Tais aspectos levam a uma maior complexidade na síntese física dessas células, incluindo restrições no uso de alguns métodos de posicionamento e roteamento (UEHARA, 1981) (IIZUKA, 2004). Ademais, apesar do número de transistores presente na rede ser uma boa métrica em nível lógico, no que tange a aspectos como área, potência e atraso (*delay*), deve-se realizar uma análise mais profunda para que se tenha uma medida precisa da qualidade da célula em nível físico.

Esse trabalho apresenta uma metodologia para geração de células a partir do método de minimização lógica baseado em grafos considerado estado-da-arte *Kernel Finder* (KF) (POSSANI, 2015). A partir das soluções geradas por esse paradigma, fez-se uma comparação com as providas pelo método de fatoração Booleana baseado em Composição Funcional (MARTINS, 2010), também considerado estado-da-arte. Vale ressaltar que a fatoração Booleana é o método amplamente utilizado para geração de bibliotecas de células utilizadas em sistemas digitais mais complexos. Através da comparação direta (caracterização) das células providas por esses diferentes paradigmas, intenta-se chegar a

conclusões quanto a qualidade das soluções geradas pelo *Kernel Finder*, dando suporte ao seu uso na síntese de circuitos e sistemas digitais mais complexos.

## 2. METODOLOGIA PROPOSTA

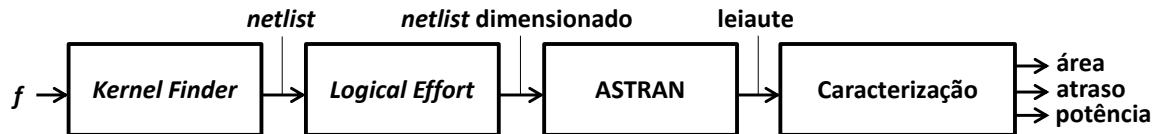

A metodologia proposta tem como objetivo prover a célula em nível físico (leiaute) a partir da rede gerada pelo KF de uma função Booleana de entrada, possibilitando a realização da caracterização elétrica. Para isso, dividiu-se a metodologia em quatro principais etapas, conforme ilustra a Figura 2.

Figura 2. Metodologia proposta.

O fluxo parte de uma função Booleana  $f$  que serve como entrada para o KF. A partir disso, desenvolveu-se um algoritmo (ilustrado na Figura 3) que gera a menor rede de transistores em termos do número de chaves passível de ser obtida via KF. Como saída desse primeiro estágio, tem-se o *netlist* contendo as interconexões dos transistores componentes da porta lógica complexa desenvolvida.

---

### Algoritmo 1 Pseudocódigo para Construção da Rede via KF

---

```

1: networkGeneration (  $F$  )

2:    $PU \leftarrow \text{kernelFinder} ( F )$

3:    $PD \leftarrow \text{kernelFinder} ( !F )$

4:   if ( isPlanar (  $PU$  ) and isPlanar (  $PD$  ) ) then

5:     if (  $PD.n < PU.n$  ) then

6:        $PU \leftarrow \text{dual} ( PD )$

7:     else then

8:        $PD \leftarrow \text{dual} ( PU )$

9:     end if

10:   end if

11:   return  $PU \cup PD$

12: end

```

---

Figura 3. Algoritmo da geração da rede de transistores via KF.

Com o *netlist* definido, utilizou o *Logical Effort* (SUTHERLAND, 1998) para realização do dimensionamento da célula. O *Logical Effort* é um método comumente aplicado para o cômputo estimado de atraso em portas lógicas complexas, bem como para o dimensionamento de transistores dessas portas. Para o último caso, a metodologia baseia-se no cálculo do caminho crítico da célula, sendo esse o fator multiplicador para definição do  $w$  dos transistores.

A próxima etapa recebe o *netlist* dimensionado e realiza a síntese física da célula. Para tanto, utilizou-se o *Automatic Synthesis of Transistor Networks* (ZIESEMER, 2014), uma ferramenta de código aberto capaz de gerar células sob demanda para diferentes tecnologias e estilos lógicos, incluindo redes NSP. O fluxo na ferramenta pode ser dividido em três partes: posicionamento de transistores, roteamento detalhado e compactação. O primeiro estágio é realizado por um algoritmo de subida de encosta (*Simulated Annealing*), enquanto o segundo usa um roteador baseado em negociação que pode ser usado para roteamento de canal. Por fim, a compactação é realizada por um algoritmo baseado no paradigma *Integer Linear Programming* (ILP). Ao final do processo, a ferramenta entrega um leiaute no estilo *linear-matrix* (1D) em formatos capazes de ser exportados para as principais ferramentas de caracterização disponíveis.

A última etapa trata da simulação e caracterização, onde a área e os atributos elétricos (atraso e potências) da porta complexa desenvolvida são levantados, sendo possível a avaliação da célula gerada a partir desses dados.

### 3. RESULTADOS E DISCUSSÃO

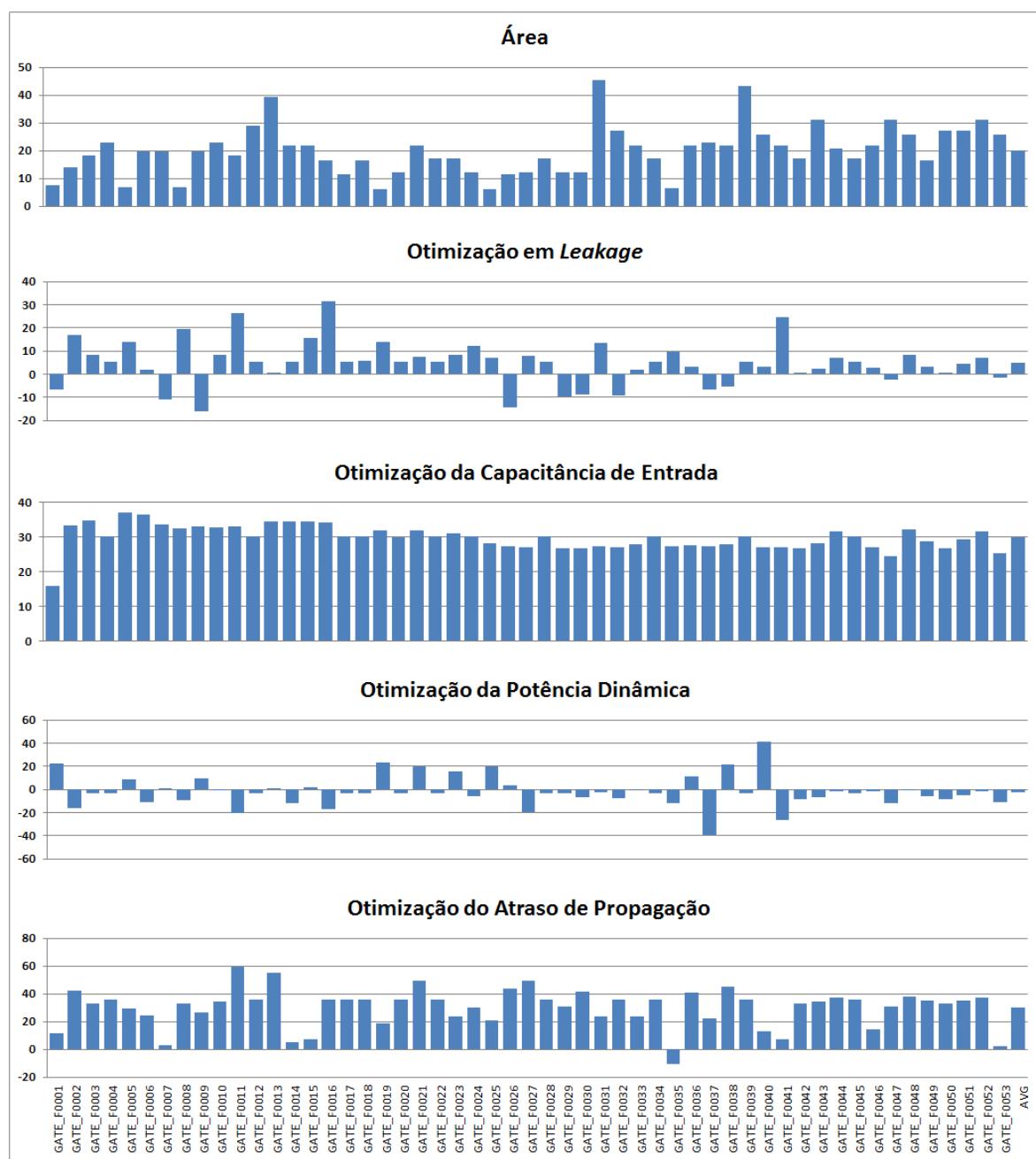

Conforme descrito na Seção 1, a metodologia proposta tem como objetivo comparar portas lógicas complexas obtidas através de dois diferentes paradigmas. Para tanto, foi utilizado um *benchmark* contendo 53 funções Booleanas comumente referenciado na literatura da área, onde cada rede de transistores foi desenvolvida seguindo a metodologia apresentada na Seção 2. A Figura 4 ilustra os resultados obtidos, onde o gráfico de barras mostra os ganhos percentuais da célula gerada pelo KF em relação a célula gerada por Composição Funcional.

Figura 4. Resultados da caracterização física das células geradas.

Como podemos notar, as células geradas pelo KF apresentaram um ganho expressivo em termos de área (20,00%) e atraso de propagação (30,22%), enquanto os aspectos relativos ao *leakage* e a potência dinâmica ficaram com valores próximos para ambas as versões geradas (4,87% e -2,14%, respectivamente). Ademais, é notável a otimização relativa as capacidades de entrada da célula (29,68%), um aspecto importante se considerarmos sistemas digitais complexos.

#### 4. CONCLUSÕES

Com os resultados obtidos, pode-se concluir que a metodologia proposta aplicada ao KF resultou em otimizações expressivas em comparação as redes geradas por Composição Funcional em termos de área, atraso de propagação e capacidade interna da célula, sendo esses alguns aspectos fundamentais para o desenvolvimento de sistemas digitais modernos.

Como trabalhos futuros, pretende-se analisar o comportamento da metodologia proposta e das células geradas quando inseridas em um sistema digital complexo, onde poder-se-á avaliar com maior precisão o impacto da redução de capacidade de entrada da célula em relação ao desempenho do sistema como um todo.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

- KAGARIS, J., HANIOTAKIS, T. A methodology for transistor-efficient supergate design. **IEEE Transactions on Very Large Scale Integration (VLSI) Systems**, vol. 15, no. 4, pp. 488-492, 2007.

- POSSANI, V., CALLEGARO, V., REIS A., RIBAS, R., MARQUES, F., DA ROSA, L. Graph-based transistor network generation method for supergate design. **IEEE Transactions on Very Large Scale Integration (VLSI) Systems**, vol. 24, no. 2, pp. 488-492, 2015.

- GOLUMBIC, M., MINTZ, A., ROTICS, U. An improvement on the complexity of factoring read-once Boolean functions. **Discrete Appl. Math.**, vol. 156, no. 10, pp. 1633–1636, 2008.

- MARTINS, M., DA ROSA, L., RASMUSSEN, A., RIBAS, R., REIS, A. Boolean factoring with multi-objective goals. **IEEE International Conference on Computer Design (ICCD)**, pp. 229-234, 2010.

- UEHARA, T. VAN CLEEMPUT, M. Optimal layout of CMOS functional arrays. **IEEE Transactions on Computers**, vol. C-30, no. 5, 305-312, 1981.

- IIZUKA, T., IKEDA, M., ASADA, K. High Speed Layout Synthesis for Minimum-width CMOS Logic Cells via Boolean Satisfiability. **Conference on Asia South Pacific Design Automation**, p.149-154, 2004.

- SUTHERLAND, I., SPROUDLL, B., HARRIS, D. **Logical Effort: Designing Fast CMOS Circuits**. Morgan Kaufmann Publishers Inc., 1998.

- ZIESEMER, A., REIS, R., MOREIRA, M., ARENDT, M., CALAZANS, N. Automatic layout synthesis with ASTRAN applied to asynchronous cells. **Latin American Symposium on Circuits and System**. p.1-4, 2014