## AVALIAÇÃO ELÉTRICA DECORRENTE DA OTIMIZAÇÃO DA TÉCNICA DE FOLDING DE TRANSISTORES MOSFET NA FERRAMENTA DE CAD ASTRAN

**GUSTAVO SMANIOTTO<sup>1</sup>; MATHEUS MOREIRA<sup>2</sup>; ADRIEL ZIESEMER JR.<sup>3</sup>;

FELIPE MARQUES<sup>1</sup>; LEOMAR DA ROSA JR.<sup>1</sup>**

<sup>1</sup>*Universidade Federal de Pelotas – {ghsmaniotto, felipem, leomarjr}@inf.ufpel.edu.br*

<sup>2</sup>*Pontifícia Universidade Católica do Rio Grande do Sul – matheus.moreira@acad.pucrs.br*

<sup>3</sup>*Instituto Federal Sul-rio-grandense – adriel.ziesemer@canoas.ifrs.edu.br*

### 1. INTRODUÇÃO

Desde sua criação, os dispositivos eletrônicos impactam desde a vida particular das pessoas até a economia das grandes empresas. Neste contexto, os circuitos integrados de aplicação específica (ASICs) ganham destaque por possuir menor área, bom desempenho e baixo consumo energético, sendo um dos responsáveis pelo avanço da microeletrônica. Contudo, produzir ASICs otimizados não é uma tarefa trivial, ainda mais quando produzidos em um processo de fabricação automática.

Atualmente, tanto na academia quanto na indústria é utilizado um processo de fabricação de circuitos integrados baseado em células padrão (ou *standard cells*) no qual, devido à sua complexidade, ferramentas de CAD (*Circuit Aided Digital*) são utilizadas no projeto destes circuitos. Neste fluxo, tanto a síntese lógica quanto a síntese física são realizadas utilizando as células presentes em uma biblioteca de células. As células contidas nestas bibliotecas são projetadas, testadas e validadas por *designers* experientes, possuindo assim, um elevado nível de qualidade e confiabilidade. Contudo, seguir este fluxo impossibilita o projetista realizar ajustes finos no projeto, sendo o número de células presentes nas bibliotecas reduzido quando comparado com o número de células possíveis (GUAN,1996), o que reduz a qualidade final do circuito.

Para contornar este problema, foi pensado em um fluxo automático de geração de layout no qual as células são geradas de acordo com a demanda do projeto. Neste estilo de geração, inicia-se o fluxo com um arquivo contendo a descrição detalhada das circuitos em nível de transistores, e ao passar pelas etapas de posicionamento, roteamento e compactação (entre outras) tanto dos transistores quanto das células, teremos o layout final do projeto. Dessa forma, pode-se produzir layouts otimizados visando otimizar diferentes problemas, como circuitos assíncronos, rápidos, *low power* (baixo consumo), dentre outros.

Uma das ferramentas seguidoras desse fluxo automático é o ASTRAN (*Automatic Synthesis of Transistor Networks*) (ASTRAN, 2015), ferramenta acadêmica de código aberto que adota esta abordagem de um fluxo automático. Com esta ferramenta é possível otimizar as células para problemas específicos, como por exemplo: circuitos assíncronos (MOREIRA,2014), redução de consumo estático, NBTI (*Negative Bias Temperature Instability*), entre outros.

Um dos passos chaves do ASTRAN é a técnica de *folding*, técnica já aplicada em outras ferramentas (CORTADELLA, 2013). Responsável por manter a altura de todas as células padrão, esta técnica consiste em “quebrar” os transistores que excedem um determinado valor limite de largura para os transistores estipulado nas regras de projeto, em quantos transistores forem necessários, sendo estes de tamanhos iguais, conectados em paralelo, de forma que a soma das alturas destes novos transistores seja igual a altura do transistor original.

### 2. METODOLOGIA

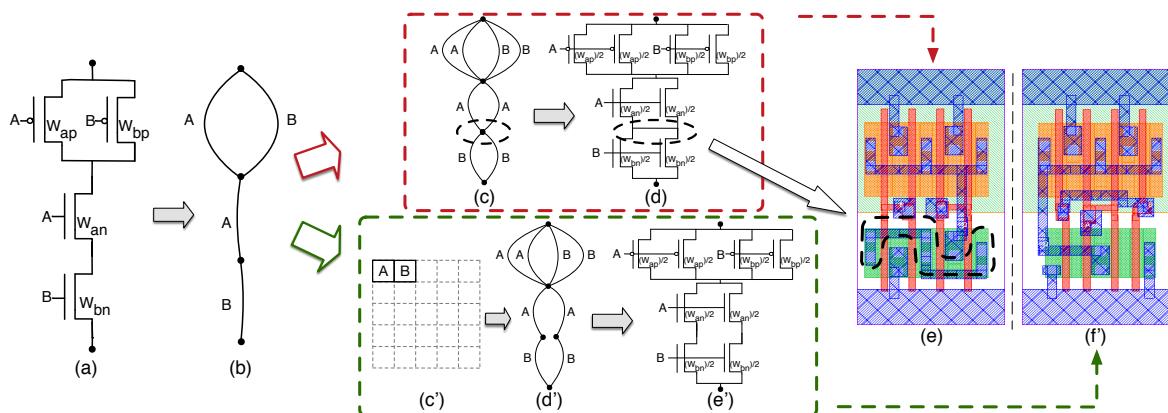

A metodologia utilizada para realizar este aperfeiçoamento à técnica de *folding* está ilustrada na **Error! Reference source not found.**. Nesta figura é apresentado a diferença entre a técnica atual implementada no ASTRAN (compreendido pela linha pontilhada vermelha) e a técnica proposta (compreendido pela linha pontilhada verde).

As duas técnicas iniciam-se da conversão do arquivo de entrada do ASTRAN, uma rede de transistores (Figura 1(a)) descrita no formato SPICE, para a estrutura de dados utilizada pela ferramenta, um grafo (Figura 1(b)), na qual cada aresta representa o terminal *gate* do transistor e cada nodo representa um terminal *source* ou *drain* do transistor.

Figura 1. Fluxo da metodologia proposta para a técnica de folding no ASTRAN.

Após esta conversão, originalmente (fluxo ilustrado pela linha pontilhada vermelha) o grafo era percorrido, e caso um transistor apresentasse o valor  $W$  (que representa a largura do transistor) maior que um determinado valor definido nas regras de projeto, este transistor era quebrado em novos transistores (chamados *legs*), que eram inseridos em paralelo no lugar do transistor original na rede de transistores, de forma que todas as *legs* obedecessem ao valor de  $W$  definido.

Para otimizar o layout final, ao invés da abordagem individual dos transistores, foi analisado as associações em série dos transistores. Assim, após a conversão da rede de transistores para um grafo, este é percorrido em busca de transistores associados em série. Para esta tarefa foi utilizada a técnica de compactação de arestas descrita em (POSSANI, 2013). Durante esta busca, as séries encontradas são armazenadas em uma matriz, na qual cada linha representa uma série, e cada coluna representa um transistor nesta série (Figura 1(c')).

Na sequência, cada série contida na matriz é analisada e caso o  $W$  de todos os transistores desta série excederem o  $W$  definido nas regras de projeto, esta série é quebrada em novas séries que são inseridas na rede de transistores, conectadas em paralelo no lugar da série original, aonde a largura dos transistores destas novas séries não excedem o valor definido nas regras e a soma da largura dos transistores presente nas novas quebras é igual a largura do transistor correspondente na série original. Por exemplo, na Figura 1(d') a série presente no grafo da Figura 1(b) foi quebrada em duas novas séries, e os dois transistores com *gate* A (Figura 1(d')) possuem  $W$  inferior ao definido nas regras de projeto e a soma destes dois valores é igual ao  $W$  do transistor com *gate* A da Figura 1(b).

Pode-se observar que a técnica atual insere conexões desnecessárias no circuito (Figuras 1(d) e (e)) que, sem elas, o funcionamento deste seria igual (Figuras 1(e') e (f')). Assim, aplicando a nova metodologia é possível otimizar o layout final, facilitando a etapa de roteamento, diminuindo o numero de contatos nas difusões e com isso, reduzindo a área total da célula e otimizando aspectos elétricos dos layouts.

### 3. RESULTADOS E DISCUSSÃO

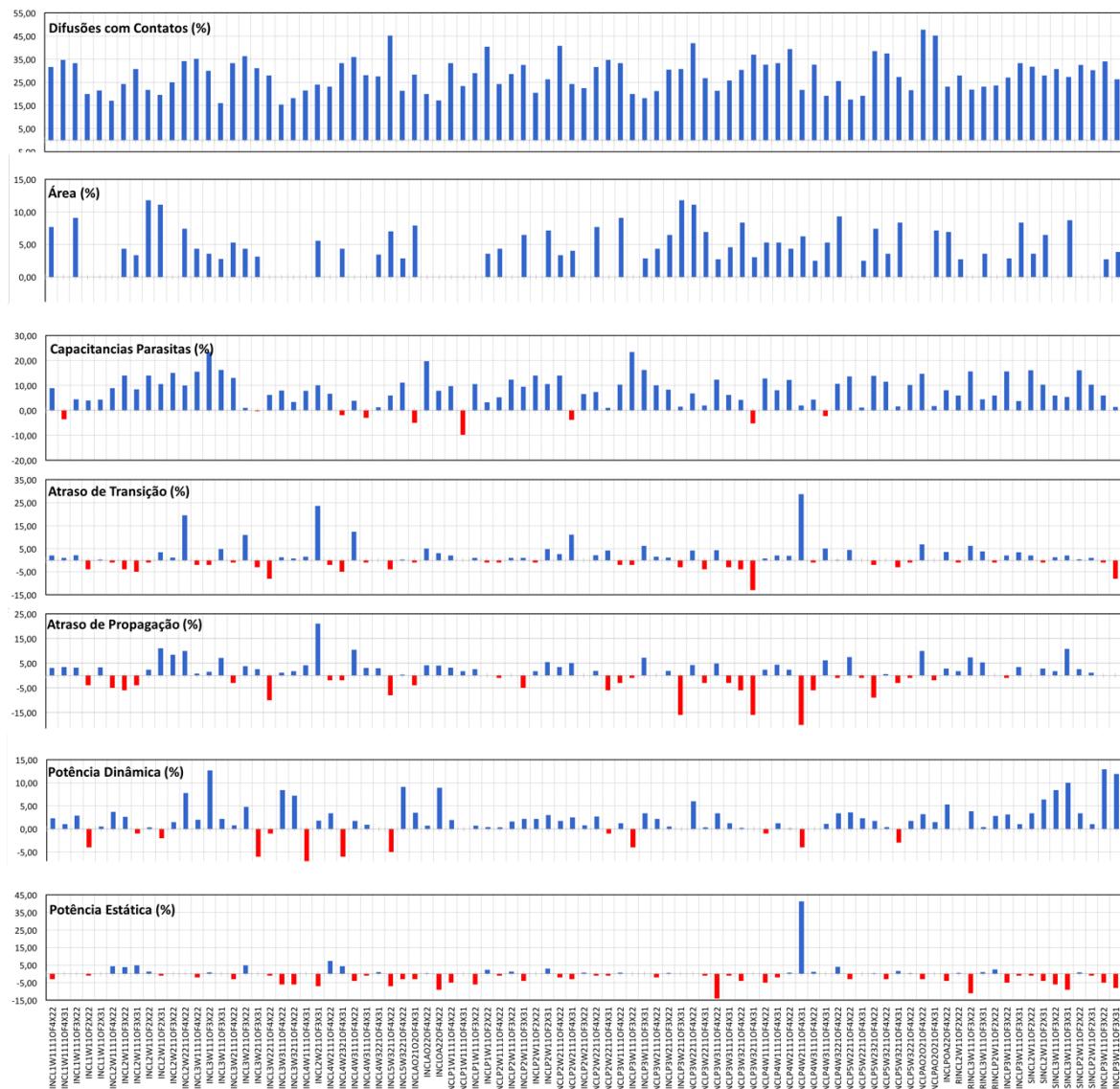

Para comparar a atual técnica e a metodologia proposta, foi selecionado um conjunto de células assíncronas utilizadas por (MOREIRA, 2014). Estas células foram submetidas ao fluxo do ASRTAN com e sem a metodologia proposta, utilizando tecnologia de 65nm. Após gerados, os layouts destas células foram comparadas em diversos aspectos, como: difusões com contatos, área, capacitâncias parasitas, atraso de propagação e transição, potência dinâmica e estática, sendo esta comparação

sumarizada na Figura 2, onde os gráficos representam a porcentagem de otimização da técnica proposta sobre a atual. Assim, as barras azuis representam otimizações e as barras vermelhas representam piora na qualidade do respectivo aspecto.

Figura 2. Resultados dos experimentos realizados.

Desta forma, nota-se que a técnica de *folding* dos transistores proposta otimizou o número de contatos nas difusões em todas as células (1º gráfico na Figura 2), resultando em uma redução média de 22,8% comparando as duas abordagens. Este dado foi obtido através da contagem das difusões que possuem contatos, como por exemplo, na Figura 1(e) existem 10 e na Figura 1(f') existem 8 difusões com contatos. Diminuindo esta quantidade de contatos, é possível aproximar os poliscilícios (linhas vermelhas nos leiautes da Figura 1) possibilitando a redução total da área do leiaute. Isso se confirma ao observar o segundo gráfico na Figura 2, na qual representa a redução de área causada pela metodologia proposta, reduzindo em média 3,75%. Tanto nas difusões com contatos quanto na área foram obtidas através do leiaute com o uso do visualizador de leiautes SightGL, e observou-se que a técnica analisando as associações em série, somente obteve ganhos em relação a técnica atual.

Na sequência, utilizando a ferramenta Calibre PEX foram extraídas as capacitâncias parasitas dos leiautes gerados. Assim sendo, o terceiro gráfico na Figura 2 representa a porcentagem de otimização da metodologia proposta contra a atual técnica de *folding* para as capacitâncias parasitas. Neste aspecto houveram somente melhorias,

sendo o pior caso de otimização em -9,8%, o melhor caso com 23,4% de otimização, porém ficando em média 7,68% de melhorias. Este aspecto recebe grande importância nas características das células pois ele está diretamente relacionado com a potencia total do leiaute.

Outros quatro aspectos foram analisados e seus valores foram obtidos com auxilio da ferramenta comercial Cadence Spectre. As simulações assumiram valores típicos de tensão e temperatura nas operações destas células, 1V e 25°C, respectivamente e, foram avaliados parâmetros de potência e atraso. Avaliando atraso de transição e propagação, ilustrado no quarto e no quinto gráfico, os melhores resultados de otimização foram de 21,1% e 26,7% respectivamente. Já os piores casos apresentaram uma piora de 20% e 13% respectivamente, ficando uma otimização média de 1,36% no atraso de transição e 0,87% no de propagação.

Quando analisada potência, temos que a potencia dinâmica foi otimizada na média, em torno de 2%, com o melhor caso sendo 12,9% e o pior caso -8% de melhoria. Já no quesito potencia estática temos o único caso em que houve perdas na média, ficando com 0,86% de piora.

#### 4. CONCLUSÕES

Neste trabalho foi desenvolvido um aprimoramento na técnica de folding dos transistores na ferramenta de CAD ASTRAN. Os resultados obtidos com os experimentos revelam que a técnica proposta otimizou os leiautes resultantes em praticamente todos os aspectos analisados (perdendo somente em um, porém a piora foi menos de 1% na média). Dessa forma, com estes resultados a nova metodologia foi integrada a ferramenta, e encontra-se disponível em (ASTRAN, 2016).

Como trabalhos futuros, planeja-se estudar os métodos de posicionamento e roteamento dos transistores nas células, tendo em vista que as três técnicas otimizadas irão produzir um leiaute próximo do ótimo.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

GUAN, B.; SECHEN, C. Large Standard Cell Libraries and Their Impact on Layout Area and Circuit Performanc. **International Conference on Computer Design, Vlsi in Computers and Processors**. Washington, DC, USA. p.378-383, 1996.

ZIESEMER JR., A. M. **Síntese Automática do Leioute de Redes de Trasistores**. 2014. Tese de Doutorado, PPGMICRO, UFRGS.

ASTRAN. **Astran – Automatic synthesis transistor networks**. Acesso em 10 ago. 2016. Online. Disponível em: <http://aziesemer.github.io/astran/>

MOREIRA, M. T., et al. Automated Synthesis of Cell Libraries for Asynchronous Circuits. **27th Symposium on Integrated Circuits and Systems Design**. p. 1-6, 2014.

CORTADELLA. J. Area-Optimal Transistor Folding 1-D Gridded Cell Design. **IEEE Transaction on Computer-Aided Design of Integrated Circuits and Systems**. v. 32, n. 11, p. 1-4, 2013.

POSSANI V., et al. Improving the methodology to build non-series-parallel transistor arrangements. **Symposium on Integrated Circuits and Systems Design**. p. 1-6, 2013.