## CARACTERÍSTICAS TOPOLOGICAS DE REDES DE TRANSISTORES GERADAS POR UMA ABORDAGEM BASEADA EM GRAFOS

REGIS ZANANDREA<sup>1</sup>; LEOMAR SOARES DA ROSA JÚNIOR<sup>1</sup>; FELIPE DE

SOUZA MARQUES<sup>1</sup>

<sup>1</sup>Universidade Federal de Pelotas – {rzanandrea, felipem, leomarjr}@inf.ufpel.edu.br

### 1. INTRODUÇÃO

Considerando o número de transistores em uma rede de transistores que é preciso para implementar uma função Booleana, abordagens baseadas em grafos vem ganhando relevância recentemente, como pode ser visto em (POSSANI, 2015) e (KAGARIS, 2007). Através da técnica de compartilhamento de caminho, esses métodos podem encontrar diversas otimizações nas redes de transistores, quando comparado com outras abordagens (MARTINS, 2010) e (DA ROSA, 2009). Por outro lado, essas abordagens baseadas em grafos podem produzir arranjos Não-Série-Paralelo (NSP), células lógicas que contém transistores conectados em bridge. Devido a ocorrência desta conexão, uma metodologia não-planar pode ser criada, conduzindo assim para a falta de dualidade e uma diferença no tamanho dos planos (plano *pull-up* e *pull-down*) da redes de transistores.

Este artigo apresenta um fluxo para identificar essas características topológicas nas redes de transistores geradas por uma metodologia baseada em grafos. Começando através de uma função booleana, é possível gerar uma rede otimizada, em termos de número de transistores, através da ferramenta estado-da-arte Kernel Finder. Esse procedimento é seguido por três testes topológicos, que são: teste de planaridade e dualidade, teste de tamanho dos planos (o qual consiste na verificação da diferença no número de transistores em cada plano da rede de transistores) e teste de *gaps* na área de difusão (que é calculado através do caminho de euler). Dessa maneira, essa metodologia fornece informações sobre todos esses impactos topológicos em funções *booleanas* amplamente usadas, permitindo uma avaliação nas redes que irá sofrer com esses aspectos, considerando seus leiaute.

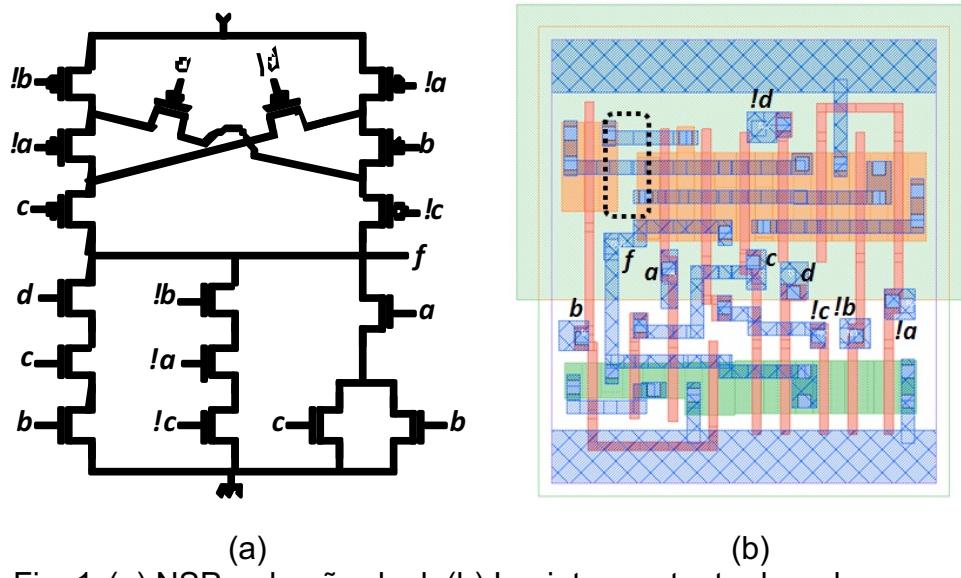

A Fig. 1 mostra um exemplo de uma rede não-serie-paralela gerada pela ferramenta Kernel Finder. Nesta rede, podemos ver a falta de planaridade e dualidade, diferença no número de transistores entre os planos lógicos e presença de caminho de euler.

Por definição, a falta de planaridade nas redes é responsável pela ocorrência da não-dualidade nos planos da rede. Sendo este aspecto uma restrição para alguns algoritmos de posicionamento, uma rede não-planar pode ser um problema para uma eficiente geração de leiaute, assim aumentando a complexidade de roteamento por causa das conexões não-planares.

Considerando a diferença no número de transistores nos planos, os impactos no leiaute é mostrados na Fig. 1 (b). Como é possível ver, existe uma diferença no tamanho dos planos *pull-up* (PU) e *pull-down* (PD). Entretando, o tamanho do leiaute é limitado pelo plano com a maior área de difusão. Também, com essa não-dualidade, a complexidade na pesquisa por casar os transistores verticalmente, o máximo compartilhamento de transistores entre os planos lógicos do leiaute, é aumentado.

Por fim, o último aspecto observado nesse artigo é a presença de *gaps* no leiaute. Os *gaps* podem ser definidos como as áreas onde dois transistores

adjacentes não podem compartilhar seus *drain/source* entre si. Isso acaba levando a um aumento no tamanho do leiaute e também no procedimento de roteamento.

Fig. 1. (a) NSP rede não-dual. (b) Leaiute resultante da rede

## 2. METODOLOGIA

Para validar os aspectos topológicos das redes de transistores, foi gerado arranjos de transistores para diferentes funções *boolenas*. Recentemente, métodos baseados em grafos vêm demonstrando que podem ser uma forma eficiente para construir arranjos de transistores otimizados. Kernel Finder é a ferramenta estado-da-arte para geração de redes de transistores otimizadas. É uma ferramenta baseada em grafos e pode criar redes NSP através da técnica de compartilhamento de caminhos. Por essa razão, foi utilizada a ferramenta Kernel Finder para gerar todas as redes deste artigo.

Entretanto, mesmo usando uma ferramenta como Kernel Finder, existem diferentes maneiras para construir os arranjos de transistores. Para gerar arranjos com o menor número de transistores produzido pela ferramenta, foi proposto o Algoritmo 1.

### 3. RESULTADOS E DISCUSSÃO

Os experimentos realizados serão apresentados nessa seção, onde foi feito sobre *benchmarks* conhecidos na literatura. O conjunto de funções é composto por NSP *handmade cells* (UFRGS, 2016), o catalogo Nimomya (HARRISON,1965), o conjunto *P-Class* (CORREIA, 2001) e o catalogo NPN5 e uma função com 11 variável. Ao total foram usadas 620563 funções *booleanas*.

A Tabela 1 mostra os resultados de planaridade e dualidade. Como podemos ver, para o *benchmark* (UFRGS, 2016) e para a função de 11 variáveis, todas as redes são ambas planares e duais. Para (HARRISON, 1965), (CORREIA, 2001) e NPN5 79,92%, 84,57% e 67,57% das redes são planares e duais, respectivamente. No oposto, considerando ambos planos não-planares, os resultados para (HARRISON, 1965), (CORREIA, 2001) e NPN5 são 12,18%, 5,90% e 7,19%, respectivamente.

A Tabela 2 mostra quantas funções (em relação a todo o *benchmark*) tem quantidade de transistores, em seus planos lógicos, diferentes. Como esperado,

no caso de redes (UFRGS, 2016) e a função de 11 variáveis, não possui diferença no tamanho dos planos. Por outro lado, para (HARRISON,1965), (CORREIA, 2001) e NPN5, 1,24%, 10,57% e 21,94% das redes, apresenta diferença na quantidade de transistores nos planos lógicos PU e PD.

Por fim, a Tabela 3 mostra o último aspecto geométrico observado nesse artigo, o *gap* na área de difusão. A tabela mostra quantas funções tem pelo menos um *gap* na área de difusão no leiaute. Como podemos ver, cerca de 28,30%, 47,51%, 57,57% e 94,02% para (UFRGS, 2016), (HARRISON,1965), (CORREIA, 2001) e NPN5, respectivamente, enquanto a função de 11 variáveis foi gerada sem *gap* na área de difusão.

| <b>Benchmark</b> | <b>Planar/dual rede (#)</b> | <b>Um plano é não-planar (#)</b> | <b>Ambos planos são não-planar (#)</b> |

|------------------|-----------------------------|----------------------------------|----------------------------------------|

| (UFRGS, 2016)    | 53                          | 0                                | 0                                      |

| (HARRISON,1965)  | 340                         | 14                               | 49                                     |

| (CORREIA, 2001)  | 3183                        | 564                              | 235                                    |

| NPN5             | 416359                      | 155435                           | 44331                                  |

| 11-input         | 1                           | 0                                | 0                                      |

Tabela 1: Resultados de planaridade e dualidade.

| <b>Benchmark</b> | <b>Funções (#)</b> | <b>Funções (%)</b> |

|------------------|--------------------|--------------------|

| (UFRGS, 2016)    | 0                  | 0                  |

| (HARRISON,1965)  | 5                  | 1.24               |

| (CORREIA, 2001)  | 421                | 10.57              |

| NPN5             | 135195             | 21.94              |

| 11-input         | 0                  | 0                  |

Tabela 2: Total de função com diferentes tamanhos nos planos.

| <b>Benchmark</b> | <b>Funções (#)</b> | <b>Funções (%)</b> |

|------------------|--------------------|--------------------|

| (UFRGS, 2016)    | 15                 | 28.30              |

| (HARRISON,1965)  | 191                | 47.51              |

| (CORREIA, 2001)  | 2133               | 53.57              |

| NPN5             | 579319             | 94.02              |

| 11-input         | 0                  | 0                  |

Tabela 3: Funções com *gaps* na área de difusão.

#### 4. CONCLUSÕES

Esse artigo propõe uma metodologia para implementação de redes de transitores através da ferramenta estado-da-arte baseada em grafo, a qual nos permite ter uma visão profunda de alguns aspectos topológicos inseridos por essa nova metodologia de geração de redes. Os testes foram realizados sobre um conjunto extensivo de *benchmarks* conhecidos na literatura e investiga três importantes aspectos no design físico: a planaridade e dualidade do arranjo, a diferença no tamanho dos planos lógicos (considerando o número de transistores) e a presença de *gaps* na área de difusão da célula.

Como trabalho futuro, se pretende continuar investigando os impactos no layout gerado por metodologias baseadas em grafos. Se pretende também, olhar outros aspectos geométricos como área e tamanho de fio, como também os comportamentos elétricos das funções, como dissipação de energia e atraso.

## 5. REFERÊNCIAS BIBLIOGRÁFICAS

POSSANI, V. ; CALLEGARO, V.; REIS, A.; RIBAS, R., MARQUES, F. ; DA ROSA, L. Graph-based transistor network generation method for supergate design. **IEEE Transactions on Very Large Scale Integration (VLSI) Systems**, vol. PP, no. 99, 2015.

KAGARIS, D.; HANIOTAKIS, T. A methodology for transistor-efficient supergate design. **IEEE Transactions on Very Large Scale Integration (VLSI) Systems**, vol. 15, no. 4, pp. 488-492, 2007.

MARTINS, A.; DA ROSA, L.; RASMUSSEN, A.; RIBAS, R.; REIS, A. Boolean factoring with multi-objective goals. **IEEE International Conference on Computer Design (ICCD)**, pp.229-234, 2010.

DA ROSA, L.; SCHNEIDER, R.; RIBAS, R.; REIS, A. Switch level optimization of digital CMOS gate networks. **ISQED 2009 Quality Electronic Design**, pp.324-329, 2009.

UFRGS. **Catalog of 53 Handmade Optimum Switch Networks**. Logics Lab, Porto Alegre, 25 jul. 2016. Acessado em 25 jul. 2016. Online. Disponível em: [http://www.inf.ufrgs.br/logics/docman/53\\_NSP\\_Catalog.pdf](http://www.inf.ufrgs.br/logics/docman/53_NSP_Catalog.pdf).

HARRISON; M. A. Introduction to Switching and Automata Theory. New York, USA: McGraw-Hill, pp. 408-472, 1965.

CORREIA, V. P.; REIS, A. Classifying n-input Boolean Functions. **Sétimo Workshop IBERCHIP**, pp. 58-66, 2001.

BOYER, J.; MYRVOLD, W. On the cutting edge: simplified O(n) planarity by edge addition. **Journal of Graph Algorithms and Applications**, vol. 8, no. 3, pp. 241-273, 2004.