## ARQUITETURA DE HARDWARE MULTIPADRÃO PARA O INTERPOLADOR DE SUBPIXEL DOS PADRÕES H.264/AVC E HEVC

GUILHERME PAIM; HENRIQUE MAICH; VLADIMIR AFONSO;

LUCIANO AGOSTINI ; MARCELO PORTO ; BRUNO ZATT

*Universidade Federal de Pelotas - Grupo de Arquiteturas e Circuitos Integrados*

*{gppaim, hdamaich, vafonso, porto, zatt}@inf.ufpel.edu.br*

### 1. INTRODUÇÃO

A tecnologia avança e cada vez mais interliga a vida das pessoas, que fazem o uso de dispositivos móveis para compartilhar seus momentos na rede. Segundo o YOUTUBE (2015), metade das visualizações é proveniente de dispositivos móveis e o Youtube recebe cerca de 300 horas de conteúdo por minuto nos seus servidores, o que equivale a 49 anos de vídeos novos em um só dia (Youtube, 2015). A CISCO (2015) estima que até o ano de 2019 o tráfego total de dados de toda a internet crescerá em dez vezes e que cerca de 90% do tráfego total será somente de vídeos digitais. Esta projeção de crescimento de tráfego é justificada pela CISCO (2015) pela inserção dos dispositivos móveis na sociedade e também pela demanda por qualidade em vídeos digitais.

Os novos dispositivos suportam diversas melhorias, dentre elas, o aumento da resolução dos vídeos, taxa de amostragem de quadros e largura de *bits* do *pixel*. Uma forma de otimizar esse tráfego previsto é a substituição do padrão de codificação, onde ganhos expressivos em taxa de compressão e qualidade podem ser atingidos ao custo de esforço computacional. Tendo em vista essa demanda, recentemente foi definido um novo padrão de codificação de vídeo, o HEVC (*High Efficiency Video Coding*) (ITU, 2013). Assim como no padrão anterior, o H.264/AVC (*Advanced Video Coding*) (ITU, 2003), diversas técnicas são utilizadas durante as etapas de codificação, visando melhores taxas de compressão com baixa perda em qualidade visual do vídeo codificado.

A grande maioria dos dispositivos móveis atuais dispõe de alto poder computacional, mas são alimentados por baterias com capacidade de energia limitada e, portanto, exigem soluções de alta eficiência energética. Arquiteturas de *hardware* dedicadas são frequentemente empregadas, devido ao alto poder de processamento que pode ser alcançado com alta eficiência energética quando comparadas com soluções não específicas como Processadores de Propósito Geral (GPPs - *General Purpose Processors*) e Unidade de Processamento Gráfico (GPUs - *Graphics Processing Units*). O projeto de sistemas de codificação e decodificação de vídeo trouxe grandes desafios para a academia e para a indústria devido à variedade de algoritmos distintos e complexos desenvolvidos para os padrões de vídeo atuais. Estes desafios aumentam quando vários padrões de codificação passam a coexistir no cenário atual.

O padrão H.264/AVC continua a ser o mais suportado nos sistemas de codificação atuais enquanto o HEVC cresce fortemente tomando espaço no mercado. A migração é impulsionada pelo aumento da taxa de compressão em 39,9%, fornecida pelo HEVC para a mesma qualidade de vídeo em comparação com o H.264/AVC (Grois, 2013). Esta migração, no entanto, ocorre gradualmente porque o H.264/AVC está presente na maioria dos sistemas e dispositivos e o HEVC é suportado apenas pelos mais recentes. Desta forma, ambos os padrões coexistirão no mercado por um longo período de tempo reforçando a necessidade para o suporte multipadrão.

Em ambos os padrões (H.264/AVC e HEVC) a Estimação de Movimento Fracionária (FME – *Fractional Motion Estimation*) é usada nos blocos de predição interquadros para reduzir as redundâncias temporais identificando os movimentos de forma mais precisa. Basicamente, a FME faz uma interpolação entre as amostras inteiras no bloco de referência, permitindo a busca em posições

fracionárias. A ferramenta que reconstrói os blocos a partir dos vetores gerados pela FME é a Compensação de Movimento (MC – *Motion Compensation*). Na MC também há uma etapa de interpolação para realizar o processo inverso ao da FME. Nos decodificadores a etapa de interpolação é responsável pelo maior esforço computacional, portanto, também possui o maior consumo de energia na etapa de decodificação. A interpolação está presente em todos os dispositivos móveis capazes de exibir vídeos e traz a maior demanda por compatibilidade o que amplia a relevância de um interpolador em *hardware multipadrão*.

Este trabalho apresenta o desenvolvimento de uma arquitetura de *hardware* para interpolação de amostras fracionárias para MC/FME com suporte aos padrões atuais, HEVC e H.264/AVC. Os objetivos específicos são: (a) processar qualquer tamanho de bloco para garantir uma alta eficiência em codificação; (b) processar vídeos em UHD (*Ultra High Definition - Ultra Alta Definição*) em tempo real; (c) foco em dispositivos móveis, portanto, com baixa dissipação de potência e menor utilização de recursos de área em relação à literatura.

## 2. METODOLOGIA

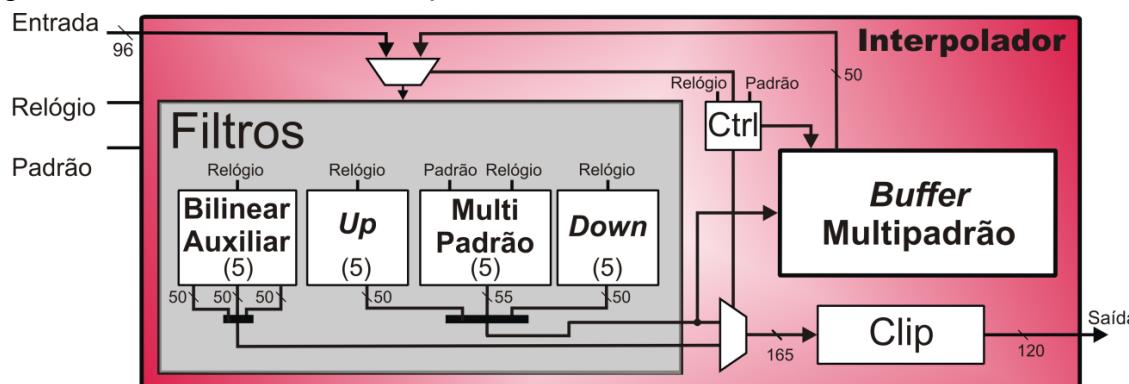

A arquitetura do interpolador multipadrão desenvolvida foi baseada nos algoritmos de interpolação de amostras de luminância definidos pelos padrões HEVC (ITU, 2013) e H.264/AVC (ITU, 2003). A partir de uma análise dos algoritmos de ambos os padrões foi proposta uma solução em *hardware* para alcançar um alto processamento aliado à eficiência energética. O interpolador desenvolvido é capaz de processar um bloco de 4x4 *pixels* inteiros a cada 31 ciclos e é composto principalmente pela filtragem e pelo *buffer* de realimentação, conforme apresentado na Figura 1. Os *buffers* são necessários para armazenar amostras fracionárias necessárias para a realimentação dos filtros com amostras previamente filtradas. Os Filtros (Figura 1) podem entregar uma linha de 15 amostras fracionárias a cada ciclo, porém, o processo de interpolação é ligeiramente diferente entre os padrões.

Figura 1 – Arquitetura de *hardware* do interpolador multipadrão.

A unidade de filtragem contém 10 filtros FIR (*Finite Impulse Response*) de 7 *taps* para a geração das amostras de quarto de *pixel* dedicados apenas ao HEVC. Esses filtros foram identificados como *Up* e *Down* (Figura 1) e previamente desenvolvidos e apresentados por AFONSO et al. (2013). As amostras de precisão quarto de *pixel* do H.264/AVC são geradas por 15 filtros bilineares (Figura 1) compostos por médias aritméticas. O interpolador, além dos filtros *Up*, *Down* e bilineares, também possui um filtro Multipadrão (Figura 1) que é capaz de gerar amostras fracionárias de meio *pixel* de precisão para ambos os padrões H.264/AVC e HEVC.

As Equações 1 e 2 representam o cálculo realizado pelos filtros Multipadrão para gerar as amostras de meio *pixel* dos padrões H.264 e HEVC, respectivamente. As entradas do Multipadrão ( $a_0$  à  $a_7$ ) são compostas por amostras inteiras de luminância provenientes do quadro de referência. A fim de

desenvolver o filtro de forma otimizada em *hardware* as Equações 1 e 2 foram fatoradas em potências de dois e seus denominadores foram igualados resultando nas Equações 3 e 4. As diferenças entre as Equações 3 e 4 foram destacadas em vermelho na Equação 4. As potências de dois foram substituídas por deslocamentos e as subexpressões foram compartilhadas para minimizar o uso dos recursos.

$$H.264 = (a_1 - 5a_2 + 20a_3 + 20a_4 - 5a_5 + a_6 + 16)/32 \quad (1)$$

$$HEVC = (-a_0 + 4a_1 - 11a_2 + 40a_3 + 40a_4 - 11a_5 + 4a_6 - a_7 + 32)/64 \quad (2)$$

$$H.264 = \{2[(a_1 + a_6) - (a_2 + a_5)] + 8[(a_3 + a_4) - (a_2 + a_5)] + 32(a_3 + a_4) + 32\}/64 \quad (3)$$

$$HEVC = \{ -[(a_0 + a_7) + (a_2 + a_5)] + 2[2(a_1 + a_6) - (a_2 + a_5)] + 8[(a_3 + a_4) - (a_2 + a_5)] + 32(a_3 + a_4) + 32 \}/64 \quad (4)$$

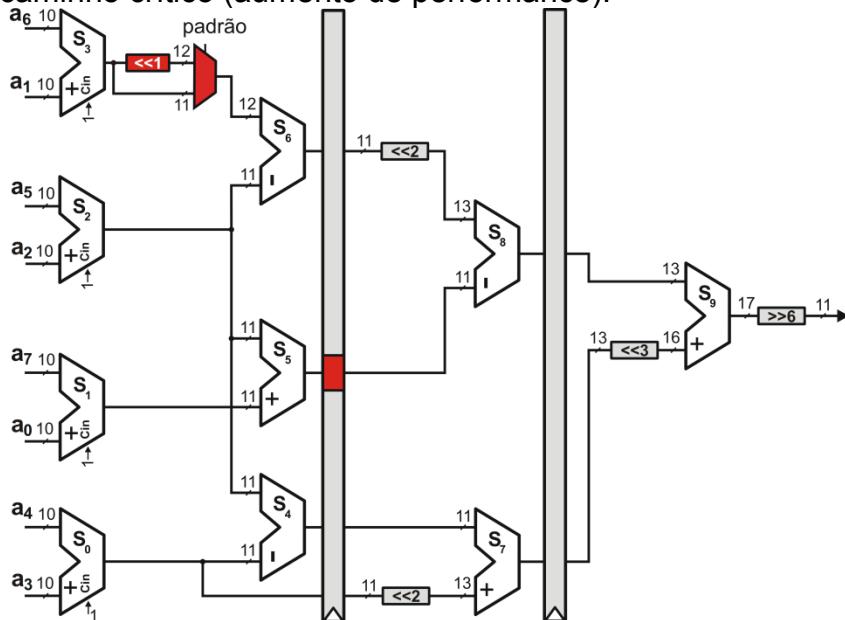

O filtro Multipadrão, apresentado na Figura 2, implementa em *hardware* as Equações 3 e 4. O filtro foi projetado com duas barreiras de *pipeline* que são necessárias para diminuir o caminho crítico e aumentar a performance de temporização. O projeto do arredondamento foi otimizado com a adição de +1 no *carry-in* dos somadores  $S_0$ ,  $S_1$ ,  $S_2$  e  $S_3$  (Figura 2). Esta operação adiciona +32 ao final do resultado e assim elimina a necessidade de um somador ao final. A otimização do arredondamento com *carry-in* proporciona diminuição de área, potência e caminho crítico (aumento de performance).

Figura 2 – Arquitetura de hardware do filtro multipadrão.

O funcionamento multipadrão foi projetado com base na eliminação de termos e pela passagem livre de multiplicações. No modo HEVC o filtro funciona de maneira completa. Já no modo H.264/AVC o filtro ativa um multiplexador de passagem livre (em vermelho na Figura 2) para retirar a multiplicação por 2. Também é aplicado um sinal de reset em um registrador de *pipeline* (em vermelho na Figura 2) para retirar o termo destacado em vermelho na Equação 4.

### 3. RESULTADOS E DISCUSSÃO

A arquitetura do interpolador multipadrão foi descrita em VHDL e sintetizada usando uma biblioteca de células padrão Nangage 45nm com a ferramenta Cadence RTL *Compiler*. Os resultados de síntese foram apresentados na Tabela 1. A contagem de *Gates* foi calculada com base em NANDs de duas entradas. A entrada da arquitetura foi chaveada com 50% de transições para avaliação da dissipação de potência com tensão de limiar de 1V. A Tabela 1 também apresenta os resultados de três trabalhos relacionados, um para H.264/AVC e dois para

HEVC. Os trabalhos relacionados não avaliam dissipação de potência, portanto, não foi possível comparação.

A solução proposta é a única solução capaz de suportar tanto H.264/AVC como o HEVC. Mesmo assim avaliando os resultados apresentados na Tabela 1, é possível concluir que supera as soluções de LIAN et al. (2006) e LIU et al. (2009) em área e taxa de processamento. A arquitetura de WANG et al. (2008) possui o dobro de processamento porém utiliza mais que o dobro da área tornando ainda a solução proposta no presente trabalho mais interessante que a referência, até mesmo porque suporta mais de um padrão de codificação.

**Tabela 1 - Resultados de síntese e trabalhos relacionados.**

| Trabalhos Relacionados  | LIU(2006) | WANG(2008) | LIAN(2009) | Desenvolvido |

|-------------------------|-----------|------------|------------|--------------|

| Padrão                  | H.264     | HEVC       | HEVC       | H.264 e HEVC |

| Tecnologia              | 130nm     | 90nm       | 90nm       | 45nm         |

| Frequência Máxima (MHz) | 350       | 280        | 193        | 965          |

| Gates (K)               | 75,74     | 64,7       | 64,5       | 31,9         |

| Potência Total (mW)     | -         | -          | -          | 12,39        |

| Taxa de Processamento   | 4k@30fps  | 8K@30fps   | 4K@47fps   | 4k@60fps     |

#### 4. CONCLUSÕES

Este trabalho apresentou uma solução em *hardware* para a interpolação de amostras fracionárias dos padrões H.264/AVC e HEVC. A arquitetura proposta também é totalmente compatível com os módulos MC e FME em ambas os padrões. Os filtros de interpolação de ambas os padrões foram comparadas e suas semelhanças foram encontradas e exploradas. A principal contribuição do presente trabalho foi o desenvolvimento de uma arquitetura de filtro multipadrão.

A arquitetura foi sintetizada usando uma biblioteca de células padrão Nangate 45nm e os resultados foram comparados com trabalhos relacionados. A arquitetura desenvolvida é capaz de processar vídeos em UHD e ocupa menos área entre os trabalhos relacionados e ao mesmo tempo é a única solução de interpolador multipadrão da literatura capaz de suportar tanto o H.264/AVC como o HEVC.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

- AFONSO, V.; et al. *Low cost and high throughput FME interpolation for the HEVC emerging video coding standard*. 4<sup>th</sup> LASCAS, 2013.

- CISCO. *The Zettabyte Era: Trends and Analysis*. Acessado em: 20 jun. 2015. Online. Disponível em: [http://www.cisco.com/c/en/us/solutions/collateral/service-provider/visual-networking-index-vni/VNI\\_Hyperconnectivity\\_WP.pdf](http://www.cisco.com/c/en/us/solutions/collateral/service-provider/visual-networking-index-vni/VNI_Hyperconnectivity_WP.pdf)

- GROIS, D.; et al. *Performance comparison of H.265/MPEG-HEVC, VP9, and H.264/MPEG-AVC encoders*. 30<sup>th</sup> PCS, 2013.

- LIAN, X.; et al. *An efficient interpolation filter VLSI architecture for HEVC standard*. 2<sup>th</sup> CHINASIP, 2014.

- LIU, J.; et al. *A full-mode FME VLSI architecture based on 8x8 and 4x4 adaptive Hadamard Transform for QFHD H.264/AVC encoder*. 19<sup>th</sup> VLSI-SOC 2011.

- ITU. *Advanced video coding Recommendation*. (H.264). International Telecommunication Union, 2003.

- ITU. *High efficiency video coding Recommendation*. (H.265). International Telecommunication Union, 2013.

- WANG, S; et al. *MC architecture for 8K UHDTV HEVC decoder*. 5<sup>th</sup> ICME, 2014.

- YOUTUBE. **Estatísticas do YouTube**. Acessado em: 20 jun. 2015. Online. Disponível em: <http://www.youtube.com/yt/press/pt-BR/statistics.html>