## EXPLORAÇÃO NO ESPAÇO DE SÍNTESE DA ARQUITETURA DA TRANSFORMADA DISCRETA DOS COSSENOS COM DIMENSÃO DE 8 PONTOS DO PADRÃO HEVC

**GIOVANNI AVILA; RUHAN CONCEIÇÃO; BRUNO ZATT; LUCIANO AGOSTINI;

MARCELO PORTO; GUILHERME CORRÊA**

*Universidade Federal de Pelotas - Grupo de Arquiteturas e Circuitos Integrados

{gdadavila, radconceicao, zatt, agostini, porto, gcorrea}@inf.ufpel.edu.br*

### 1. INTRODUÇÃO

Dada a recente popularização dos vídeos digitais, os quais demandam um elevado fluxo de dados, faz-se cada vez mais necessário o uso de técnicas de compressão de vídeo para transmitir e armazenar os mesmos. Este crescimento na demanda é proveniente de novas tecnologias como *smartphones*, *tablets* e também de uma maior popularização de serviços de *streams* online. Em 2014, 64% dos dados que trafegaram na internet provieram de reproduções de vídeos digitais e a previsão é de que esse número aumente para 80% até o ano de 2019 (CISCO, 2015).

Considerando esta situação, em 2011, especialistas em codificação de vídeo da ITU-T e da ISO/IEC formaram o grupo *Joint Collaborative Team on Video Coding* (JCT-VC) (JCT-VC, 2012), no qual iniciaram o projeto de um novo padrão de codificação de vídeos, denominado *High Efficiency Video Coding* (HEVC) (HEVC, 2013). Este padrão foi lançado em janeiro de 2013 e atualmente é considerado o estado da arte em codificação de vídeos, pois consegue duplicar a taxa de compressão do vídeo quando comparado com o seu antecessor, o padrão H.264/AVC (ITU-T, 2014), mantendo a mesma qualidade de imagem. Entretanto, para alcançar este propósito, o novo padrão faz uso de diversas técnicas de compressão de vídeo de alta complexidade computacional. Assim, como soluções puramente em software podem não propiciar a codificação de vídeos em tempo real (pelo menos 30 quadros por segundo), há uma demanda por projetos de hardware para os módulos que compõem o codificador.

O HEVC segue um modelo híbrido de codificação de vídeos, assim como o H.264/AVC, no qual há um estágio inicial de predição intra-quadro e inter-quadros, seguido pelas etapas de transformada, quantização e codificação de entropia (SULIVANN et al., 2012). Dentre os módulos que compõem o codificador HEVC, destaca-se o módulo das transformadas, o qual é responsável por transformar os resíduos de predição do domínio espacial para o domínio das frequências. A principal transformada dentro do codificador é a Transformada Discreta dos Cossenos (*Discrete Cosine Transform* – DCT), a qual tem quatro tamanhos estipulados no padrão HEVC ( $4 \times 4$ ,  $8 \times 8$ ,  $16 \times 16$  e  $32 \times 32$ ).

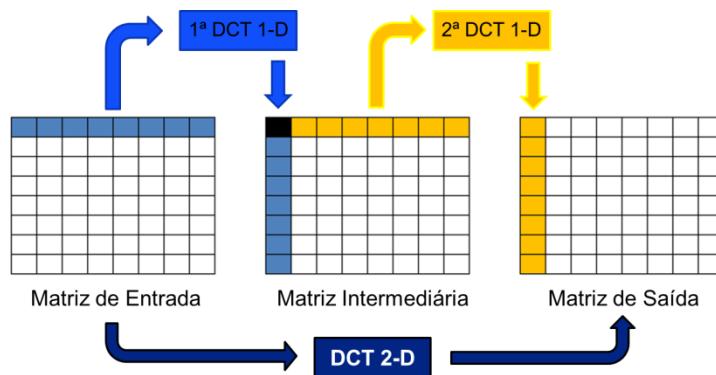

Para que a transformada em duas dimensões (2D) seja aplicada, uma transformada de uma dimensão (1D) é aplicada linha a linha na matriz de entrada, e o resultado é salvo coluna a coluna em uma matriz intermediária. Após isto, o mesmo processo é aplicado linha a linha na matriz intermediária e o resultado é salvo coluna a coluna na matriz de saída. Este tipo de processamento é possível devido o princípio da separabilidade apresentado pelas DCTs. A Figura 1 ilustra este processo para uma DCT  $8 \times 8$ .

Figura 1: Implementação da DCT 2D através da aplicação de múltiplas DCTs 1D.

Este trabalho apresenta um projeto de hardware para a transformada DCT 1D de 8 pontos do padrão HEVC. Além disso, este trabalho também apresenta uma exploração no espaço de síntese da arquitetura, onde diversas famílias de dispositivos *Field-Programmable Gate Array* (FPGA) da Altera (ALTERA, 2015) são comparadas após a síntese do projeto de hardware da DCT 1D de 8 pontos em termos de número de elementos lógicos e pinos utilizados, tempo de propagação do caminho crítico e frequência máxima de operação da arquitetura.

A seção 2 apresenta o processo de análise realizado sobre o software de referência do codificador HEVC, o tratamento realizado sobre o algoritmo da transformada e o projeto final da arquitetura. Logo em seguida, a seção 3 apresenta os resultados do projeto de hardware e da análise de espaço de projeto realizada neste trabalho. Por fim, são apresentadas as conclusões e inovações trazidas pelo trabalho.

## 2. METODOLOGIA

O funcionamento da DCT foi observado através da análise do software de referência do HEVC (*HEVC Model – HM*) em sua versão 16.5 (JCT-VC, 2015). Neste software, grande parte das funções opera de maneira conjunta, não estando prontas para funcionarem de maneira independente. Assim, o primeiro passo foi identificar a função que implementa a transformada estudada e modificá-la a fim de fazê-la funcionar isoladamente. Foram necessárias ainda outras modificações no código, já que a função inicialmente seria aplicada em todas as linhas da matriz e o objetivo deste trabalho é analisa-la para apenas 8 pontos (uma linha).

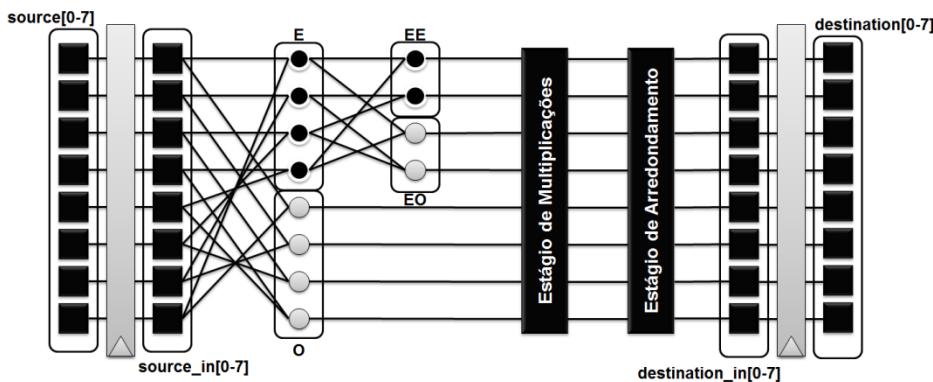

Após o estudo e análise da transformada DCT, a sua arquitetura foi descrita em VHDL utilizando a ferramenta Quartus II (versão 13) da Altera (ALTERA, 2015). A Figura 2 apresenta um diagrama de blocos desta arquitetura que demonstra o cálculo da coluna de saída da DCT (*destination*). A figura mostra o diagrama de blocos simplificado da arquitetura implementada, onde *source[x]* representa a amostra de entrada na posição *x* e *destination[y]* representa a amostra de saída na posição *y*. As duas barras em cinza são barreiras de registradores adicionadas com o objetivo de possibilitar a análise de desempenho da arquitetura. Os blocos “E”, “EE”, “O” e “EO” representam conjuntos de operadores, onde os círculos de cor preta são os somadores e os de cor cinza são os subtratores.

Figura 2: Diagrama de blocos simplificado da arquitetura implementada para o cálculo da DCT de 8 pontos.

Visando efetuar a análise no espaço de projeto de síntese, a arquitetura foi sintetizada em 10 diferentes famílias de FPGA da Altera, sendo elas as famílias Cyclone II, III, III LS, IV E, IV GX, V, Arria II, MAX II e MAX V. A partir de dados fornecidos pela ferramenta Quartus II, foram colhidas informações a respeito de diversos aspectos da arquitetura sintetizada, como o número de elementos lógicos e a frequência de operação.

### 3. RESULTADOS E DISCUSSÃO

Para validar a arquitetura descrita, foram utilizados valores de entrada e de saída obtidos com o software de referência e comparados com os gerados pela arquitetura. Assim, o software de referência foi utilizado como um *golden model*. Em todos os casos testados, os valores foram equivalentes.

Os resultados de síntese obtidos com a arquitetura sintetizada para os diversos dispositivos estão apresentados na Tabela 1. As famílias que começam com C (CII, CIII, CIII LS, CIV E, CIV GX e CV) são as pertencentes à família Cyclone. Além disso, resultados de desempenho, medidos em números de quadros por segundo (qps) para resolução *High Definition 1080p* (HD 1080p – 1920×1080 pixels) e *Ultra High Definition 4K* (UHD 4K – 3840×2160 pixels), também são apresentados na Tabela 1.

As comparações demonstradas na tabela apresentam o comportamento da arquitetura proposta pelo trabalho em todas as arquiteturas suportadas pela ferramenta Quartus II. O número total de elementos lógicos (*Total Logic Elements* – TLE) na arquitetura sintetizada é 1.234 elementos. Como este número é independente da família em que a arquitetura está sintetizada, o valor absoluto é igual para todas elas. A mesma observação é válida para o número absoluto de pinos utilizados (*Pins*), que é igual a 233 em todos os casos.

Tabela 1: Resultados de síntese da arquitetura para diversas famílias de FPGA.

| Parâmetro        | Família FPGA |      |         |       |        |      |          |        |       |

|------------------|--------------|------|---------|-------|--------|------|----------|--------|-------|

|                  | CII          | CIII | CIII LS | CIV E | CIV GX | CV   | Arria II | MAX II | MAX V |

| TLE (%)          | 9            | 8    | 2       | 8     | 4      | <1   | 3        | 61     | 61    |

| Pins (%)         | 74           | 67   | 79      | 68    | 76     | 87   | 58       | 86     | 86    |

| Registradores    | 224          | 224  | 224     | 224   | 224    | 244  | 224      | 224    | 244   |

| Freq. Máx. (MHz) | 74,3         | 80,1 | 68,4    | 80,2  | 80,1   | 57,7 | 108,6    | 44,1   | 34,7  |

| HD 1080p         | 191          | 206  | 175     | 206   | 206    | 148  | 279      | 113    | 89    |

| UHD 4K qps       | 47           | 51   | 43      | 51    | 51     | 37   | 69       | 28     | 22    |

Nota-se que, com exceção das famílias MAX, a quantidade de elementos lógicos utilizados foi bem pequena em relação ao total disponível nos dispositivos. Este fato, entretanto, não se repetiu com relação ao número total de pinos utilizados; em todos os casos foi utilizada uma parte significativa do total disponível. A frequência do sistema, medida em MHz, é referente ao maior atraso possível da arquitetura, ou seja, é a frequência máxima de operação.

Considerando os resultados de desempenho, observa-se que a arquitetura é capaz de processar vídeos de resolução HD 1080p em tempo real (30 qps pelo menos) em qualquer uma das famílias de FPGA. Além disso, considerando a resolução UHD 4K, a qual exige uma maior taxa de processamento e quadros por segundo para dar sensação de movimento ao telespectador (60 qps), apenas a síntese na família Arria II GC atingiu a taxa de processamento necessária.

#### 4. CONCLUSÕES

Este trabalho apresentou o desenvolvimento de hardware para a DCT de 8 pontos do padrão HEVC de codificação de vídeos. Além disso, o trabalho também apresentou uma exploração do espaço de projeto de síntese, onde diversas famílias de FPGA da Altera foram comparadas para o hardware desenvolvido.

Os resultados de síntese mostraram que a utilização de elementos lógicos pela arquitetura foi quase sempre abaixo de 10%, exceto nos FPGAs da família MAX. Os resultados de desempenho apontaram que a arquitetura é capaz de processar vídeos HD 1080p em tempo real quando sintetizada para qualquer família de FPGA explorada neste trabalho. Considerando vídeos de resolução UHD 4K, apenas a síntese no FPGA da família Arria II GC atingiu o desempenho necessário. Como trabalho futuro, espera-se expandir este estudo para os demais tamanhos de DCT definidas no padrão HEVC (4x4, 16x16 e 32x32) e explorar alternativas arquiteturais com o objetivo de possibilitar o processamento de vídeos UHD 4K em tempo real.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

- Cisco. **Visual Networking Index: Forecast and Methodology, 2014–2019**, 2015. Acessado em 19 de Julho de 2015. Online. Disponível em: [http://www.cisco.com/c/en/us/solutions/collateral/service-provider/ip-ngn-ip-next-generation-network/white\\_paper\\_c11-481360.html](http://www.cisco.com/c/en/us/solutions/collateral/service-provider/ip-ngn-ip-next-generation-network/white_paper_c11-481360.html)

- JCT-VC. **JCT-VC - Joint Collaborative Team on Video Coding**. 2012. Acessado em 19 de Julho de 2015. Online. Disponível em: <http://www.itu.int/en/ITU-T/studygroups/2013-2016/16/Pages/video/jctvc.aspx>.

- JCT-VC. High Efficiency Video Coding text specification draft 10, doc. JCTVC-L1003, Genebra, Suíça, 2013.

- ITU-T. Recommendation H.264/AVC (02/14): advanced video coding for generic audiovisual services. [S.I.], 2014.

- SULLIVAN, G.; OHM, J.; HAN, W.-J.; WIEGAND, T. Overview of the High Efficiency Video Coding (HEVC) Standard. Circuits and Systems for Video Technology, IEEE Transactions on, [S.I.], v.22, n.12, p.1649–1668, Dec 2012.

- ALTERA. **The Leader in Custom Logic Solutions**. Acessado em 19 de Julho de 2015. Online. Disponível: <https://www.altera.com/about/company/overview.html>

- JCT-VC of ITU-T SG16 WP3 and ISO/IEC JTC1/SC29/WG11 – High Efficiency Video Coding (HEVC) Test Model 16 (HM 16) Improved Encoder Description Update 2, Fevereiro 2015.