## ANÁLISE COMPARATIVA EM NÍVEL LÓGICO DE DIFERENTES IMPLEMENTAÇÕES DA FUNÇÃO OU-EXCLUSIVO

RAPHAEL DORNELLES<sup>1</sup>; MATEUS BECK FONSECA<sup>2</sup>

<sup>1</sup>*Universidade Federal de Pelotas – raphael.dornelles@ufpel.edu.br*

<sup>2</sup>*Universidade Federal de Pelotas – mateus.fonseca@ufpel.edu.br*

### 1. INTRODUÇÃO

Uma das funções lógicas de maior utilização em circuitos aritméticos é a função ou-exclusivo (XOR) (FLOYD, 2007). Circuitos aritméticos são utilizados em diversos tipos de aparelhos digitais, no processamento digital de sinais, como microcomputadores, tablets e celulares (TOCCI, 2007). A busca por melhores resultados no desenvolvimento de topologias para funções lógicas, resulta na ampla oferta de topologias na literatura que utilizam diferentes arquiteturas de implementação e diferentes quantidades de componentes em seus circuitos. Este trabalho tem como objetivo reunir diferentes implementações de funções lógicas XOR e verificar a sua eficiência em nível lógico.

### 2. METODOLOGIA

Admitindo que uma Tabela Verdade (TV) é uma tabela matemática utilizada na lógica, especificadamente em álgebra Booleana, funções Booleanas, e no cálculo de expressões lógicas funcionais em cada um de seus argumentos funcionais, ou seja, em cada combinação de valores tomados pela suas variáveis lógicas (ENDERTON, 2001), esta pode ser utilizada para validação lógica de determinada função.

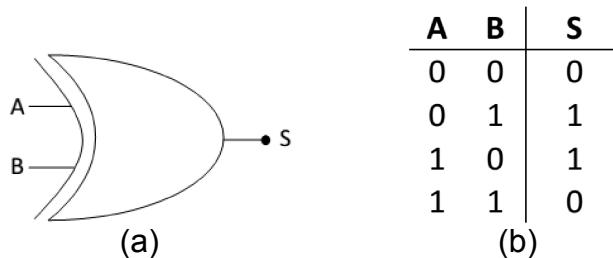

Neste estudo é verificada a validação lógica de diferentes topologias de funções lógicas XOR, a qual possui representação gráfica e TV com seu devido funcionamento conforme a Figura 1, sendo na TV identificado o nível lógico baixo como '0' (zero) e nível lógico alto como '1' (um).

Conhecida como ou-exclusivo ou disjunção exclusiva, esta função lógica compara dois operandos de entrada, A e B respectivamente, e impõe na sua saída (S) nível lógico alto, se e somente se, apenas um dos dois operandos estiver em nível lógico alto, caso contrário tal saída terá nível lógico baixo.

Figura 1 – Representações da função XOR: (a) Simbologia e (b) Tabela Verdade

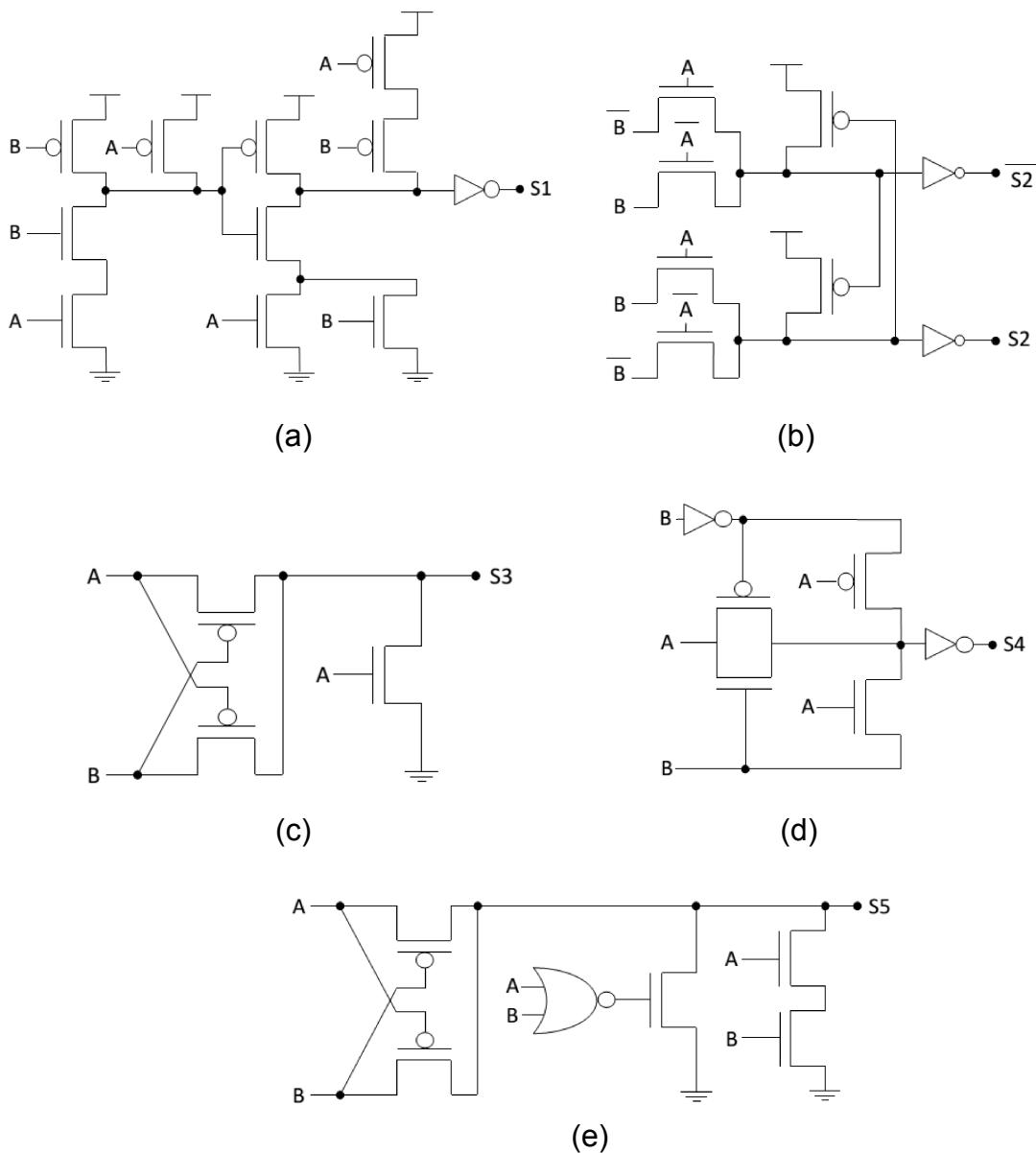

Na Figura 2 são apresentadas as diferentes topologias da porta XOR encontradas na literatura, dentre estas estão presentes arquiteturas de implementação CMOS (Semicondutor complementar de metal óxido, do inglês:

*Complementary Metal Oxide Semiconductor) e CPL (Lógica de transistor de passagem complementar, do inglês: *Complementary Pass transistor Logic*). Muitas outras topologias também foram encontradas na literatura, como por exemplo: (GOEL, 2006) e (WANG, 1994), contudo são baseadas nas topologias apresentadas na Figura 2. A validação lógica do funcionamento destas foi obtida através da implementação e simulação com a versão acadêmica do programa DSCH ver.3.5.11 (MICROWIND).*

Figura 2 - Topologias portas XOR verificadas (a) CMOS (CHANDRAKASAN, 1995), (b) CPL (CHANDRAKASAN, 1995), (c) MVT (DHAR, 2014), (d) CMOS\* (CHANDRAKASAN, 1995) e (e) mista (FONSECA, 2011)

### 3. RESULTADOS E DISCUSSÃO

Na Figura 3 são apresentadas as saídas (via TV) das topologias da Figura 2, sendo possível verificar que a implementação MVT (item (c) da Figura 2) não apresenta funcionalidade para toda a TV. Quando as entradas A e B, recebem respectivamente '1' (nível lógico alto) e '0' (nível lógico baixo), é esperado

conforme comportamento desta função lógica, que na sua saída (S) esteja o nível lógico alto ('1'), no entanto nível lógico baixo ('0') é encontrado.

| A | B | S1 |

|---|---|----|

| 0 | 0 | 0  |

| 0 | 1 | 1  |

| 1 | 0 | 1  |

| 1 | 1 | 0  |

(a)

| A | B | S2 | $\bar{S2}$ |

|---|---|----|------------|

| 0 | 0 | 0  | 1          |

| 0 | 1 | 1  | 0          |

| 1 | 0 | 1  | 0          |

| 1 | 1 | 0  | 1          |

(b)

| A | B | S3 |

|---|---|----|

| 0 | 0 | 0  |

| 0 | 1 | 1  |

| 1 | 0 | 0  |

| 1 | 1 | 0  |

(c)

| A | B | S4 |

|---|---|----|

| 0 | 0 | 0  |

| 0 | 1 | 1  |

| 1 | 0 | 1  |

| 1 | 1 | 0  |

(d)

| A | B | S5 |

|---|---|----|

| 0 | 0 | 0  |

| 0 | 1 | 1  |

| 1 | 0 | 1  |

| 1 | 1 | 0  |

(e)

Figura 3 – Tabelas verdade das topologias de função XOR apresentadas na Figura 2; (a) CMOS, (b) CPL, (c) MVT, (d) CMOS\* e (e) mista

#### 4. CONCLUSÕES

Este trabalho analisou cinco topologias distintas de funções XOR, comparando-as no programa de simulação DSCH versão acadêmica, e obtendo a TV de cada implementação. Como mostrado nem todas as topologias da literatura apresentam boa funcionalidade, desta forma é visto a importância da simulação de uma topologia desejada para uma utilização em um sistema digital.

Das topologias analisadas, a topologia (c) da Figura 2 não apresenta funcionalidade completa. Para melhor diferenciação e análise das topologias, um estudo de simulação analógica sobre os circuitos apresentados é indicado como seguimento a este trabalho.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

CHANDRAKASAN, A. P; BRODERSEN, R. W. **Low Power Digital CMOS Design**. Norwell, MA: Kluwer, 1995.

DHAR, K., Design of a low power, high speed and energy efficient 3 transistor XOR gate in 45nm technology using the conception of MVT methodology, **Control, Instrumentation, Communication and Computational Technologies (ICCICCT), 2014 International Conference**, vol., no., pp.66,70, 10-11 July 2014.

ENDERTON, H. **A Mathematical Introduction to Logic**, 2<sup>nd</sup> edition. San Diego: Harcourt/Academic Press, 2001.

FLOYD, T. **Sistemas Digitais: Fundamentos e Aplicações**. 9<sup>a</sup> ed. São Paulo: Artmed, 2007.

FONSECA, M.; COSTA, E; MARTINS, J. Design of power efficient butterflies from radix-2 dit fft using adder compressors with a new xor gate topology, **Analog Integrated Circuits and Signal Processing**, vol. 73, no. 3, pp. 945–954, 2012. Disponível em: <http://dx.doi.org/10.1007/s10470-012-9952-2>.

GOEL, S.; ELGAMAL, M.A.; BAYOUMI, M.A. Novel design methodology for high-performance XOR-XNOR circuit design, **Integrated Circuits and Systems Design, 2003. SBCCI 2003. Proceedings. 16th Symposium**, vol., no., pp.71,76, 8-11 Sept. 2003.

**MICROWIND, DSCH Schematic Editor & Digital Simulator.** Acessado em 20 jul. 2015. Disponível em: <http://www.microwind.net/dsch.php>.

TOCCI, R. J.; WIDMER, N.S.; MOSS, G.L. **Sistemas Digitais: Princípios e Aplicações**. 10<sup>a</sup> ed. São Paulo: Pearson, 2007.

WANG, J.M; FANG, S.C; FENG, W.S. New efficient designs for XOR and XNOR functions on the transistor level, **Solid-State Circuits, IEEE Journal**, vol.29, no.7, pp.780,786, Jul 1994.