## DESENVOLVIMENTO DE UM ALGORITMO PARA ASSINATURA DE CÉLULAS NA FERRAMENTA FLEXMAP

JOÃO JÚNIOR DA SILVA MACHADO<sup>1</sup>; JULIO SARAÇOL DOMINGUES JUNIOR<sup>2</sup>

LEOMAR SOARES DA ROSA JR<sup>3</sup>; FELIPE DE SOUZA MARQUES<sup>4</sup>

<sup>1</sup>Universidade Federal de Pelotas – jjdsmachado@inf.ufpel.edu.br

<sup>2</sup>Universidade Federal do Pampa – Campus Bagé – juliodomingues@unipampa.edu.br

<sup>3</sup>Universidade Federal de Pelotas – leomarjr@inf.ufpel.edu.br

<sup>4</sup>Universidade Federal de Pelotas – felipem@inf.ufpel.edu.br

### 1. INTRODUÇÃO

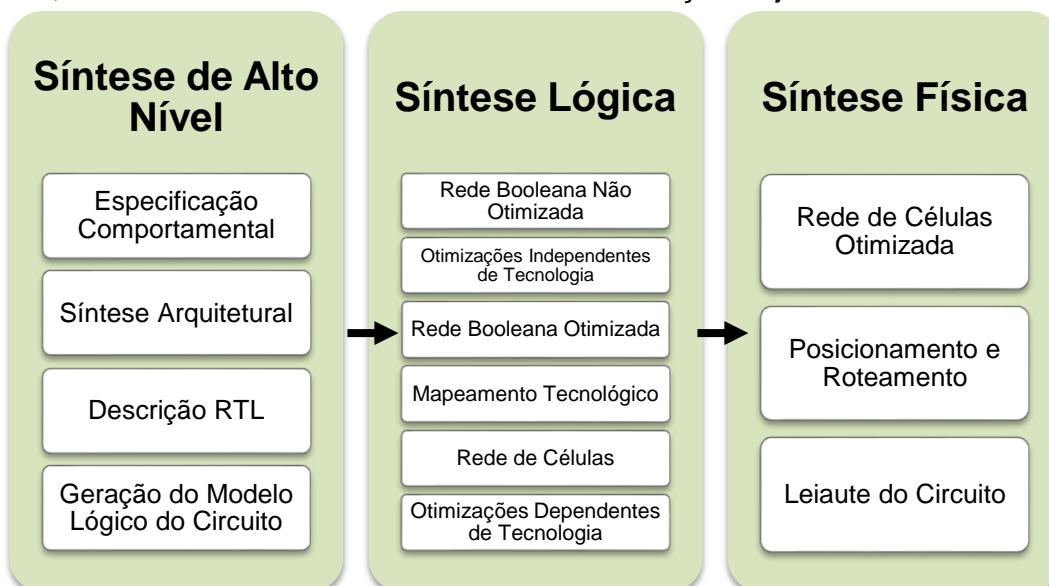

Devido a popularização da microeletrônica nos últimos anos, o projeto de circuitos *Very Large-Scale Integration* (VLSI) é considerado cada vez mais exigente, uma vez que é preciso desenvolver circuitos que apresentem ao mesmo tempo, maior desempenho e menor consumo de energia. Como pode ser visto na Figura 1, existem diversas fases que envolvem o projeto de um Circuito Integrado. Contudo, é na etapa de mapeamento tecnológico, dentro da síntese lógica, que se pode explorar melhor as otimizações no circuito. Isso porque nesta etapa são definidas quais células serão utilizadas para compor o circuito final. O mapeamento transforma uma descrição lógica de um circuito (rede booleana) em uma representação composta por instâncias interconectadas de elementos de uma biblioteca de células.

Segundo Marques (MARQUES, 2007), o processo de mapeamento pode ser dividido em três etapas: Decomposição, Identificação de Padrões e Cobertura Lógica. A primeira etapa visa preparar a estrutura de dados para o mapeamento, gerando uma representação do circuito. Normalmente, esta estrutura de dados utiliza apenas um conjunto restrito de operadores lógicos. Em um segundo momento, aplica-se a identificação de padrões, também conhecida como casamento. Esta etapa visa verificar a equivalência entre subgrafos e células de uma biblioteca. Este processo normalmente irá resultar em algumas sobreposições de células, o que acarretará em um aumento de área no circuito final. Para solucionar este problema, aplicam-se algoritmos de cobertura, com o intuito de definir o melhor conjunto de células que será utilizado para implementar o circuito, de forma a satisfazer uma determinada função objetivo.

Figura 1. Etapas realizadas durante o processo de síntese de circuitos VLSI.

O presente trabalho possui foco voltado para a etapa de identificação de padrões, mais precisamente no processo de identificação da equivalência das células de uma determinada biblioteca de células com as porções do circuito em questão. Biblioteca de células é um conjunto finito de portas lógicas onde cada elemento da biblioteca implementa a funcionalidade de uma função lógica e possui algumas características elétricas próprias. Essas características serão importantes no momento da escolha da porta lógica de acordo com a função objetivo e podem ser referentes a área, atraso, consumo de potência, etc.

Existem diversas formas para se efetuar o processo de verificação de equivalência de células, dentre elas, pode-se citar: verificação estrutural, verificação booleana e verificação por restrição. A verificação estrutural (em inglês, *structural matching*), costuma-se ser aplicada quando o mapeamento utiliza biblioteca de células estáticas. Utilizando a representação em grafos de cada elemento da biblioteca, algoritmos para isomorfismos de grafos são aplicados com intuito de realizar a equivalência entre as células da biblioteca com as porções do circuito, como pode ser visto em (CHATTERJEE, 2005). Já a verificação booleana (em inglês, *Boolean matching*), é feita quando parte do circuito é funcionalmente equivalente à função booleana implementada por uma célula. Um exemplo deste tipo de verificação pode ser encontrado em (MAILHOT, 1990). Por fim, na verificação por restrição, aplica-se um conjunto de restrições nas porções do circuito. Essas restrições são características topológicas que a porção do circuito a ser mapeada precisa respeitar, como por exemplo, o número de entradas de uma porta lógica.

O objetivo deste trabalho é proporcionar na ferramenta FlexMap o processo de equivalência de células através da verificação estrutural. A ferramenta FlexMap foi desenvolvida na Universidade Federal de Pelotas (FLEXMAP, 2015) e possui algumas estratégias e estruturas de dados que permitem a configuração de diferentes fluxos de síntese para realizar o mapeamento tecnológico. Desta forma, é possível desenvolver dentro do ambiente FlexMap, fluxos alternativos de mapeamento e aplicar diferentes métodos de síntese, utilizando a estrutura de dados e o algoritmo de cobertura lógica desejados.

## 2. METODOLOGIA

O presente trabalho possui como objetivo principal desenvolver um algoritmo para a etapa de identificação de padrões que é realizada durante o processo de mapeamento tecnológico. O algoritmo a ser desenvolvido será voltado para verificações estruturais durante o processo de identificação de padrões. O objetivo principal da abordagem proposta é permitir que os métodos de mapeamento da ferramenta FlexMap considerem bibliotecas de células mais complexas, viabilizando assim novos resultados de mapeamentos.

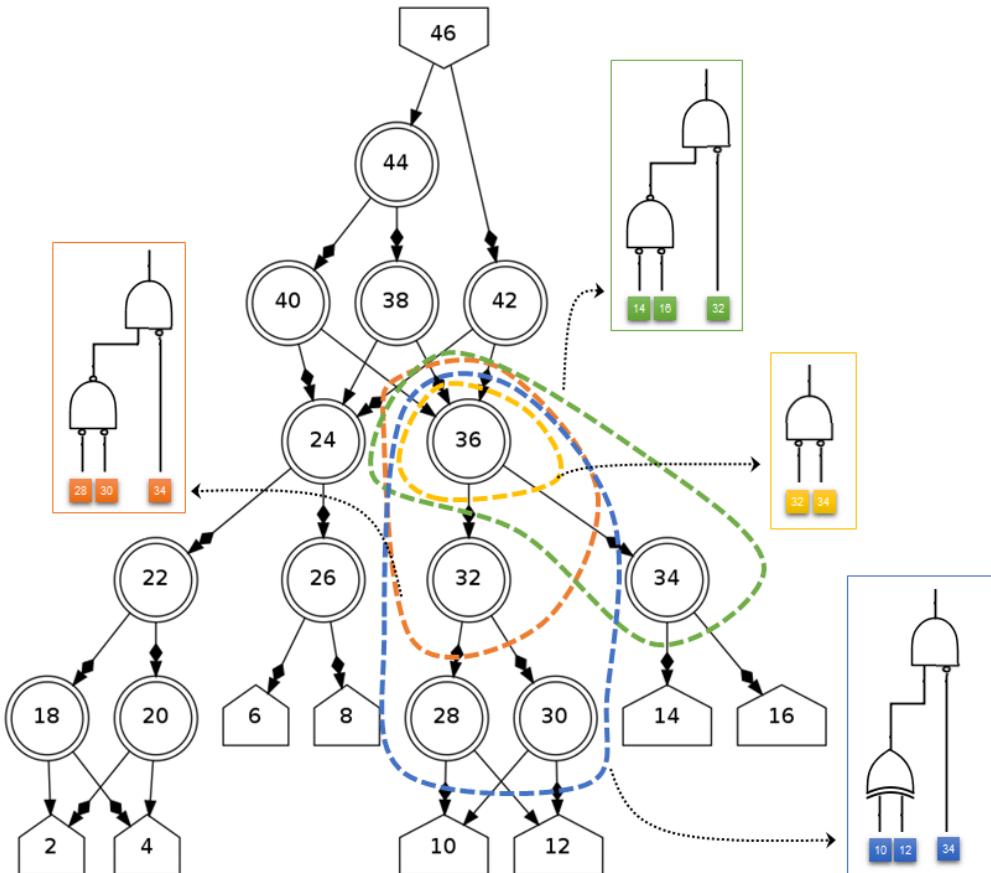

A etapa de identificação de padrões visa encontrar porções (células) no circuito equivalentes as células disponíveis na biblioteca de células. Cada equivalência encontrada será candidata a compor o conjunto final de células necessárias para a construção do circuito (MARQUES, 2007). Um exemplo desta etapa é ilustrado na Figura 2, onde é representado possíveis equivalências que podem ser obtidas para o nodo 36 utilizando no máximo três entradas.

O objetivo da etapa de identificação de padrões é determinar se um porção da descrição sujeito pode ser implementada por uma célula disponível na biblioteca, sendo por isso considerada uma etapa crítica realizada durante o mapeamento (CORREIA, 2004). Dependendo do tamanho da biblioteca e do tamanho do circuito (número de nodos no grafo), essa etapa pode possuir alto custo computacional na execução do método de mapeamento. Neste sentido,

investigar e propor novas metodologias para esta etapa, pode viabilizar otimizações consideráveis no tempo de execução de uma ferramenta de síntese lógica. Essa investigação tentará identificar as principais necessidades de um novo método de assinatura de células considerando a abordagem de verificação estrutural. Este tipo de abordagem verifica a existência de grafos isomórficos entre as células do circuito e a biblioteca de células. Para isso, tanto a descrição sujeito quanto as células da biblioteca precisam ser decompostas da mesma forma.

Figura 2. Possíveis equivalências obtidas para o nodo 36

### 3. RESULTADOS E DISCUSSÃO

Atualmente, a ferramenta FlexMap é limitado a abordagem de métodos de verificação Booleanos para etapa de identificação de padrões. Este tipo de método normalmente apresenta melhores resultados quando comparados a abordagem de verificação estrutural, pois não dependem da estrutura que representa o circuito. Entretanto, os métodos Booleanos costumam ser mais custosos em tempo. Por essa razão, alguns métodos trabalham com funções de poucas variáveis, o que não é suficiente para vários casos práticos. Neste caso, algoritmos estruturais são utilizados. Sendo assim, este trabalho possui como motivação avaliar as técnicas atuais para assinatura de células utilizando verificação estrutural e, então, através desta análise, desenvolver um método que possibilite utilizar biblioteca de células mais complexas na ferramenta FlexMap.

Neste primeiro momento, está sendo realizado uma revisão bibliográfica acerca dos métodos existentes e técnicas que poderão ser combinadas, visando obtenção de melhores resultados de mapeamento tecnológico na ferramenta FlexMap. Combinado com a etapa de revisão bibliográfica, está se realizando o desenvolvimento do algoritmo proposto. Em fase intermediária de desenvolvimento, espera-se concluir o mesmo em breve e então, realizar uma

série de testes e simulações, comparando a eficácia do algoritmo desenvolvido com os métodos mais recentes para abordagem de verificação estrutural, disponíveis na literatura.

#### 4. CONCLUSÕES

A partir do desenvolvimento deste algoritmo, será possível alcançar melhores resultados de mapeamento. A funcionalidade permitirá utilizar bibliotecas de células com diferentes números de entradas, quando comparado a abordagem de verificação Booleana que se tem implementado na ferramenta FlexMap atualmente. Com isso, o FlexMap poderá considerar diferentes arranjos de células no momento de mapeamento. Desta forma, espera-se otimizar os resultados de mapeamentos até então obtidos no FlexMap, além de propiciar um ambiente mais genérico de mapeamento, possibilitando o uso de células com um maior número de entradas.

Para verificar a eficácia do algoritmo após seu desenvolvimento, diversas comparações com métodos estado-da-arte serão realizados. As comparações irão utilizar *Benchmarks* conhecidos da área, como por exemplo ISCAS'85 (BRGLEZ, 1985) e IWLS 2005 (ALBRECHT, 2005). A importância deste trabalho se deve ao fato de que além de otimizar os resultados de mapeamento, a implementação irá contribuir para obter uma ferramenta acadêmica com diferentes fluxos de mapeamento, permitindo comparação entre os métodos e metodologias disponíveis na literatura.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

ALBRECHT, C., "IWLS 2005 Benchmarks" published at 2005 **International Workshop on Logic Synthesis**, June 2005.

BRGLEZ, F. , FUJIWARA, H. "A Neutral Netlist of 10 Combinational Benchmark Circuits and a Target Translator in Fortan", in **Proc. of the International Symposium on Circuits and Systems**, 1985, pp. 663-698.

CHATTERJEE, S.; MISHCHENCKO, A.; BRAYTON, R.; WANG, X.; KAM, T., "Reducing structural bias in technology mapping," Computer-Aided Design, 2005. **ICCAD-2005. IEEE/ACM International Conference on** , vol., no., pp.519,526, 6-10 Nov. 2005.

CORREIA, V.; REIS, A., "Advanced technology mapping for standard-cell generators," **Integrated Circuits and Systems Design**, 2004. SBCCI 2004. 17th Symposium on , vol., no., pp.254,259, 7-11 Sept. 2004.

**FLEXMAP. FlexMap Um novo Framework para Mapeamento Tecnológico.** Acessado em 09 de jul. de 2015. Online. Disponível em: [http://inf.ufpel.edu.br/gaci/?page\\_id=597](http://inf.ufpel.edu.br/gaci/?page_id=597).

MAILHOT, F.; DE MICHELI, G., "Technology mapping using Boolean matching and don't care sets," Design Automation Conference, 1990., EDAC. **Proceedings of the European** , vol., no., pp.212,216, 12-15 Mar 1990.

MARQUES, F. S.; ROSA JR, L. S.; RIBAS, R. P.; SAPATNEKAR, S. S.; REIS, A. I. 2007. DAG based library-free technology mapping. In **Proceedings of the 17th ACM Great Lakes symposium on VLSI (GLSVLSI '07)**. ACM, New York, NY, USA, 293-298.