## APLICAÇÃO DA TÉCNIKA TÊMPERA SIMULADA NO PROBLEMA DO MAPEAMENTO TECNOLÓGICO

MATHEUS G. NACHTIGALL<sup>1</sup>; JÚLIO S. DOMINGUES JR.<sup>2</sup>; FELIPE S. MARQUES<sup>3</sup>; PAULO R. FERREIRA JR.<sup>4</sup>

<sup>1</sup>Universidade Federal de Pelotas – mgnachtigall@inf.ufpel.edu.br

<sup>2</sup>Universidade Federal de Pelotas - jsdomingues@inf.ufpel.edu.br

<sup>3</sup>Universidade Federal de Pelotas - felipem@inf.ufpel.edu.br

<sup>4</sup>Universidade Federal de Pelotas - paulo@inf.ufpel.edu.br

### 1. INTRODUÇÃO

Atualmente existe uma grande demanda de desenvolvimento de técnicas para automação do processo de concepção dos circuitos integrados, com o principal objetivo de reduzir o tempo de projeto do circuito. Embora muitos avanços na área de concepção de circuitos integrados tenham sido desenvolvidos nas últimas décadas, projetar circuitos eficientes ainda não é uma tarefa trivial. O Problema do Mapeamento Tecnológico (PMT) é o passo da síntese lógica de circuitos que escolhe quais portas lógicas serão usadas na implementação de um leiaute em uma dada tecnologia (MARQUES, 2008). Esta etapa de mapeamento tem um grande impacto na estrutura do circuito e, consequentemente, no seu desempenho e área.

O mapeamento tenta encontrar a melhor configuração para implementar um circuito, utilizando algum critério de minimização. Este critério pode ser área, atraso ou consumo de energia, entre outros. Tratando-se de atraso ou consumo já existem soluções conhecidas em tempo polinomial ou linear (MANOHARARAJAH et al., 2006). Entretanto, quando se trata de minimização de área em circuitos com mais de 3 entradas, o problema é considerado *NP-Difícil*. Dessa forma, são utilizadas heurísticas para atingir resultados sub-ótimos ou ótimos nessa minimização.

A técnica de Têmpera Simulada (TS), amplamente conhecida na área de inteligência artificial, demonstra bons resultados quando aplicada em problemas de otimização. Este artigo apresenta uma implementação desta técnica para a solução do PMT, buscando a minimização de área do circuito. Foram executados diversos experimentos utilizando um subconjunto comumente utilizado na área para testes de desempenho. Esse subconjunto pertence a um pacote de benchmarks amplamente conhecido da área (BRYAN, 1985). Os testes iniciais sobre os benchmarks mostram que a técnica de TS é promissora para o PMT.

Na seção seguinte, será mostrado os conceitos do mapeamento tecnológico e a abordagem desenvolvida para a etapa de cobertura utilizando a técnica de TS. Por fim, serão apresentados os resultados, conclusões e trabalhos futuros.

### 2. METODOLOGIA

O mapeamento tecnológico pode ser dividido em 3 etapas principais: *decomposição*, *casamento* e *cobertura*. Dada a descrição inicial do circuito, é necessário preparar a estrutura de dados que o represente para a etapa de mapeamento. Esta estrutura de dados é também chamada de *Descrição sujeito*. A *decomposição* têm como objetivo principal organizar a representação inicial através da *Descrição sujeito*. Grafos são descrições fortemente utilizadas para esta representação, principalmente os *Grafos Acíclicos Direcionados* (DAG) e uma de suas especializações chamada *And-Inverter-Graph* (AIG). Este formato consegue

decompor a lógica do circuito em duas portas primitivas: *And* e *Inversores*, e é fortemente utilizado nas ferramentas atuais.

Na etapa de *casamento* ocorre uma identificação de padrões entre subgrafos do AIG com os elementos da tecnologia alvo. Esta etapa enumera todas as possibilidades de casamento para cada nodo do AIG, para uso futuro na etapa de cobertura.

A etapa de *cobertura* têm como objetivo selecionar o melhor conjunto de células para a implementação final do circuito. Dessa forma, após gerar todos os casamentos possíveis, esta etapa tenta definir quais dos casamentos serão combinados para a solução final. Para isso existem diversas técnicas que podem ser aplicadas, como programação dinâmica e estratégias gulosas. A etapa de cobertura se torna importante dentro do processo de mapeamento, pois é responsável por encontrar a configuração que melhor corresponda a função custo e que diminua as áreas de sobreposição no circuito.

A técnica de Têmpera Simulada (KIRKPATRICK et al. 1983) é uma técnica de otimização baseada no processo metalúrgico de resfriamento de metais. A cada etapa da técnica, o algoritmo tenta trocar a solução atual por uma solução vizinha. A nova solução poderá ser aceita com base em uma probabilidade calculada com base nos valores da solução e de um parâmetro “temperatura”, que diminui constantemente durante a execução do algoritmo. Quando a temperatura está alta, o algoritmo permite trocas mais frequentes nas soluções, expandindo o espaço de busca e evitando soluções ótimas globais. Com a redução da temperatura, o algoritmo reduz a probabilidade de escolhas inferiores a atual, caminhando em direção a uma solução ótima global. Foi realizada uma adaptação desta técnica para a etapa de cobertura do PMT. Neste caso, a função objetivo do TS procura minimizar o número de componentes utilizados em uma cobertura do circuito.

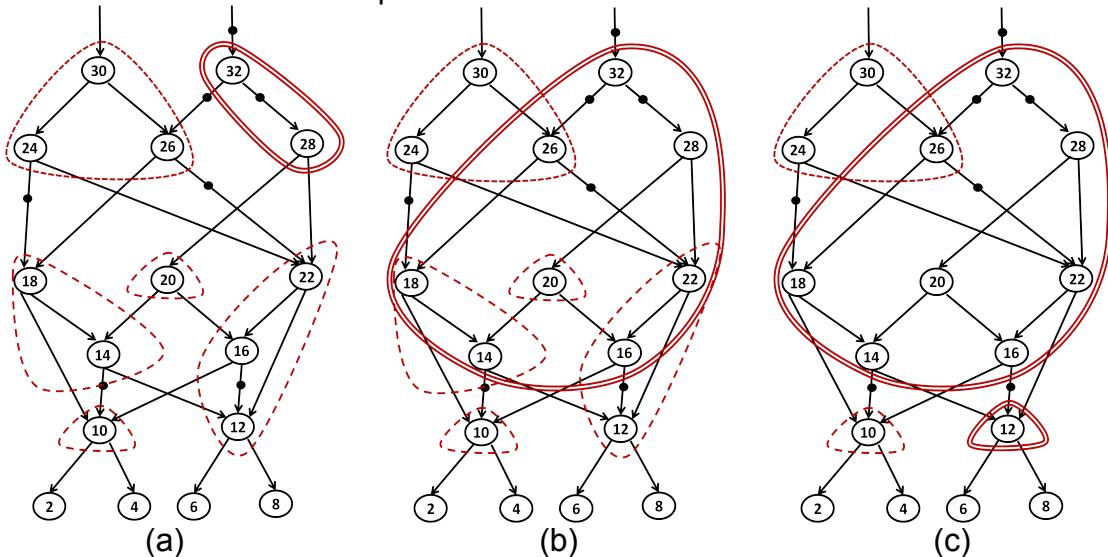

Figura 1: Iteração da técnica Têmpera Simulada

Após a etapa de casamento, a técnica gera uma cobertura inicial do AIG. Um componente é escolhido aleatoriamente para cobrir cada nodo do AIG e seu subgrafo, independente da ocorrência de sobreposição. Depois que todos os nodos foram cobertos, é feita uma busca em profundidade no grafo para eliminar coberturas duplicadas e redundantes. Esta etapa é chamada de limpeza.

Terminado o procedimento de limpeza, o processo básico do TS inicia. A Figura 1 mostra a execução de uma iteração da técnica desenvolvida. A cada passo

do algoritmo um nodo do grafo é escolhido aleatoriamente para que ocorra a modificação da sua cobertura, como mostra a Figura 1(a). Um componente diferente é escolhido aleatoriamente para substituir a atual (Figura 1(b)). Depois da substituição, é necessário refazer a etapa de limpeza, verificando se a troca não gerou dependências ou coberturas desnecessárias. O resultado deste procedimento pode ser visualizado na Figura 1(c).

A cada iteração do algoritmo, a temperatura do sistema decai levemente, a uma taxa de 0.1% por iteração, permitindo assim uma quantidade significativa de iterações para que a técnica consiga convergir para uma solução favorável a partir da solução gerada aleatoriamente. A técnica implementada utilizou duas funções de avaliação para o problema: a primeira foi baseada no algoritmo clássico de TS, onde inicia-se o algoritmo com uma temperatura alta e a técnica é executada até que a temperatura atinja um valor pré-definido, normalmente muito próximo a zero; a segunda abordagem, que está sendo proposta aqui, foi implementada após análise de comportamento do algoritmo, controlando a temperatura da simulação para obter uma probabilidade de aceitação de no máximo 25% e executando o algoritmo até não detectar nenhuma mudança de estados em um grande número de iterações.

### 3. RESULTADOS E DISCUSSÃO

Os resultados foram obtidos através da execução de experimentos na ferramenta FlexMap. As descrições de entrada são fornecidas utilizando um subconjunto do pacote de benchmarks ISCAS'85 (BRYAN, 1985). Para verificar a eficiência da técnica implementada, 30 simulações foram executadas com cada benchmark do subconjunto para cálculos de média. Cada simulação iniciou-se em um estado inicial aleatório, para que fosse possível verificar a capacidade de otimização do TS.

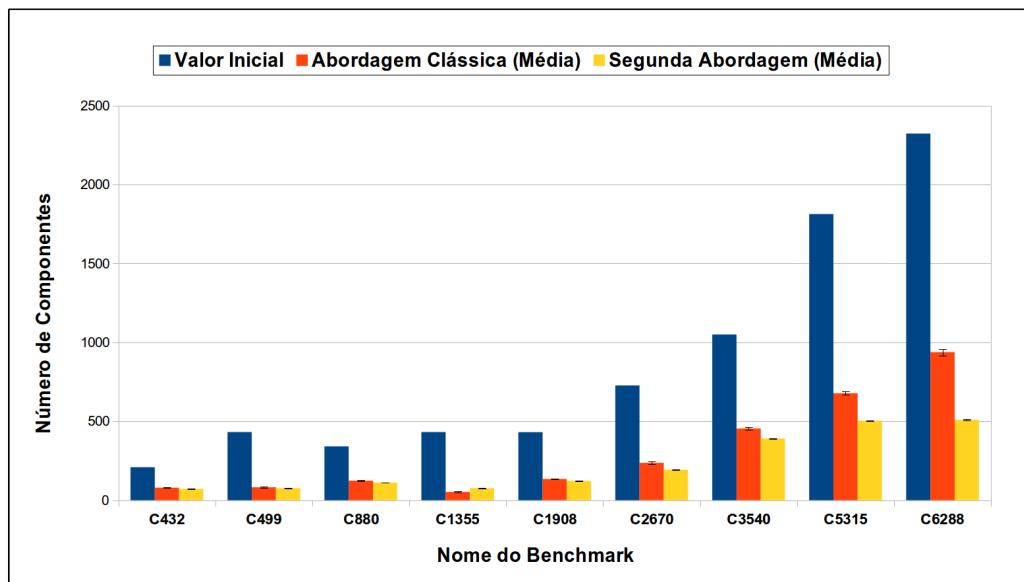

Figura 2: Desempenho do TS em comparação com o valor inicial

A Figura 2 mostra a comparação da média de componentes necessária para a cobertura do AIG tanto na cobertura inicial como na média dos valores após a aplicação da otimização do TS. A técnica de TS clássica resultou em melhorias de pelo menos 55% sobre os valores iniciais em todos os benchmarks avaliados, apresentando melhorias de até 84% em alguns benchmarks.

O segundo conjunto de experimentos realizados mostrou melhorias significativas, gerando resultados pelo menos 62% melhores em todos os casos avaliados em comparação com o estado inicial. Em alguns benchmarks, a melhora registrada foi de até 84%. A Tabela 1 mostra a média dos valores de todos os benchmarks executados em ambos experimentos, junto com o desvio padrão e o percentual de melhora em média dos mesmos benchmarks sobre o estado inicial.

|              | <b>Valor Inicial</b> | <b>Abordagem Clássica (Média)</b> | <b>Desvio Padrão</b> | <b>Segunda Abordagem (Média)</b> | <b>Desvio Padrão</b> |

|--------------|----------------------|-----------------------------------|----------------------|----------------------------------|----------------------|

| <b>C432</b>  | 209                  | 79.13 ( <b>62.14%</b> )           | 2.91                 | 71.53 ( <b>65.77%</b> )          | 0.81                 |

| <b>C499</b>  | 432                  | 82.10 ( <b>81.00%</b> )           | 2.79                 | 76.17 ( <b>82.37%</b> )          | 1.19                 |

| <b>C880</b>  | 341                  | 123.50 ( <b>63.78%</b> )          | 3.42                 | 111.67 ( <b>67.25%</b> )         | 1.14                 |

| <b>C1355</b> | 432                  | 52.03 ( <b>81.01%</b> )           | 2.76                 | 76.27 ( <b>82.35%</b> )          | 1.03                 |

| <b>C1908</b> | 431                  | 134.47 ( <b>68.80%</b> )          | 3.00                 | 122.30 ( <b>71.62%</b> )         | 1.27                 |

| <b>C2670</b> | 727                  | 236.70 ( <b>67.44%</b> )          | 6.45                 | 192.90 ( <b>73.47 %</b> )        | 1.64                 |

| <b>C3540</b> | 1050                 | 454.13 ( <b>59.61%</b> )          | 7.17                 | 391.00 ( <b>62.76%</b> )         | 1.95                 |

| <b>C5315</b> | 1813                 | 677.93 ( <b>62.61%</b> )          | 11.53                | 503.87 ( <b>72.21%</b> )         | 2.72                 |

| <b>C6288</b> | 2323                 | 938.17 ( <b>59.61%</b> )          | 21.01                | 509.14 ( <b>78.08%</b> )         | 3.68                 |

Tabela 1:Média dos resultados, porcentagens e desvio padrão dos benchmarks

#### 4. CONCLUSÕES

Este trabalho apresentou um novo método para resolver o Problema do Mapeamento Tecnológico. O método é baseado na técnica de têmpera simulada e consegue obter soluções promissoras para a cobertura de circuitos integrados.

Em trabalhos futuros, pretende-se expandir os experimentos para avaliar todos os benchmarks do pacote ISCAS'85 para melhor avaliar a eficiência da técnica implementada. Pretende-se também comparar as soluções aqui obtidas com as consideradas estado-da-arte na área de Mapeamento Tecnológico. Finalmente, planeja-se utilizar essas soluções consideradas estado-da-arte como ponto de partida do algoritmo de Têmpera Simulada, ao invés da solução inicial aleatória, buscando otimizar ainda mais os resultados.

#### 5. REFERÊNCIAS BIBLIOGRÁFICAS

MARQUES, F. d. S. **Technology Mapping for Virtual Libraries Based on Cells with Minimal Transistor Stacks**. 2008. Tese (Doutorado em Computação) – Curso de Pós-Graduação em Computação, Universidade Federal do Rio Grande do Sul.

MANOHARARAJAH, V.; BROWN, S.; VRANESIC, Z. Heuristics for area minimization in LUT-based FPGA technology mapping. **Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on**, v. 25, n. 11, p. 2331-2340, 2006.

BRYAN, David. The ISCAS'85 benchmark circuits and netlist format. **North Carolina State University**, 1985.

KIRKPATRICK, Scott; JR., D.. Gelatt ; VECCHI, Mario P. Optimization by simulated annealing. **science**, v. 220, n. 4598, p. 671-680, 1983.